# 1988 DATA BOOK

# **Late Definition Technologies**

Through the use of special late definition technologies, products can be tailored to meet an exact application after wafer fabrication is complete. Modifications may be made either by the Company or in the field by the user. Certain products are also capable of self-modification based on feedback information.

#### **Embedded Lithium Power Sources:**

Dallas Semiconductor has the ability to integrate in a single package, its ultra low power CMOS circuits and a miniature lithium power source. Chips designed in this way can accept change and remember data throughout their operating life.

#### **Direct Laser Writing:**

Lasers provide a low cost means for Dallas Semiconductor to routinely alter, reconfigure, or program individual chips after completion of wafer fabrication. Proprietary software controls the laser to make each chip unique.

#### High Energy Ion Implantation:

Circuits on nearly finished wafers are defined to exact customer specifications. Using a millionvolt implanter, wafers are bombarded by a cloud of super charged ions. The ions penetrate specific layers of silicon to economically tailor chips to specific functions.

not the only name behind our products . . .

1

Cathy Broch Seam 7. Crawlay Manarat Bohmore back Francis an their 3Am CHIHIM Dugan Bals Michael And Did June Henry Thomas Jr. allow Than Delleyper Ken Meruhi Albourn Than Delleyper Ken Meruhi Anton Labor allow - Ana E. Cong m Bill F tome Mars de Peo Hate Ch goe Blac Mein Sty Bavier amin . John dig. - Himny Comed Schundt Spengflow to-Phil Alan 3.Gil oan Hall dalf met adama Harry Scarlynaugh John Monton Mart Mail le quelochain Chris Neumon Loy 1 Low Steven L. Cannel Folkes Jongh a Tues Fam Joiner / Melado- Bru  $\alpha$ Laures Jopana Calts R. Ton nas Harrington Joren 15 tan shell LARRy Adves Warn Kanello Wayn. pause U in teach Mandon ancy Lee Karry & Hatton Vache Pays Man 16 Robert Lenel ROBEIEN L.C. Jandlig Kha Duong F.I. SHAH Mena. Toat hend Recenta Blue John Robut lanto 1 men gore - Dia Sider 5 anniel Klum ame a. LAT ! 'en Alala erry Barbara alderate Halle Vinn S. Quin Higher me finness a Porr . taraban min Pullin / - On dreuts TUOI TRINH BAUM DENG Vanda Jos Lanto Yanah Tol. Jaroh 1 E. Chanageralt Mar ai ng K.Bem " Lay our How alugform to SOFIA TAN FYAZ Haybuthitmph annarath P.a. Ab gurle Such Fun aling Celan Manus opitot Phary Chum forg Scor Krin ha Hamela Siah Mic AVUNSIENCY Drulys Suong Tran asa Ini pries Boran Cha. Pating La John Kahfelott fund Dr. Lehard Daniel Spechak Jaon Michall. Habert nolly Holem . J. When the ar el Jonne softer dinen Thran ear Sthuon MRound Fralle 6. nat Melia ROB SMITH alistrary Margo Mose Jerry Besty to the rafanz. 1 emp go that Mitch Kayala Dorasol Stepsher M. Curn John Wantan R. Helen J. Wilson Kelm Donald X. Hourton imme) SE. Robert 1 Vergue my ( Kita an allam al Kim Sel UN Un A Honer Human (In) I and IAC hamparati ett ( Johnson Buddy amet TryetNgo Danknep Oran anenner AD o Spersur Doo na manarit Diane Vasauez

# **Dallas Semiconductor**

| <b>General Information</b> | 1  |

|----------------------------|----|

| Silicon Timed Circuits     | 2  |

| <b>Multiport Memory</b>    | 3  |

| Microcontroller            | 4  |

| Nonvolatile Static RAM     | 5  |

| Intelligent Sockets        | 6  |

| Timekeeping                | 7  |

| User Insertable Memory     | 8  |

| Security Products          | 9  |

| Integrated Battery Backup  | 10 |

| System Extension           | 11 |

| SipStik™ Products          | 12 |

| <b>Wireless Products</b>   | 13 |

| Telecommunications         | 14 |

| MODEM                      | 15 |

| <b>Application Notes</b>   | 16 |

|                            |    |

3

# **Table of Contents**

#### **GENERAL INFORMATION**

| Product List         | 9  |

|----------------------|----|

| Corporate Fact Sheet | 11 |

| Sales Offices        | 13 |

| Representatives and  |    |

| Distributors         | 13 |

| Product Overview     | 19 |

### PRODUCT DATA SHEETS

### **Silicon Timed Circuits**

| DS1000 5-Tap Silicon Delay Line  | 30 |

|----------------------------------|----|

| DS1005 5-Tap Silicon Delay Line  | 38 |

| DS1007 7-in-1 Silicon Delay Line | 46 |

| DS1010 10-Tap Silicon Delay Line | 53 |

| DS1013 3-in-1 Silicon Delay Line | 60 |

| DS1015 Constant Density Data     |    |

| Separator                        | 68 |

#### **MultiPort Memory**

| DS2009 512 × 9 FIFO         | 70 |

|-----------------------------|----|

| DS2010 1K × 9 FIFO          | 71 |

| DS2011 2K × 9 FIFO          | 72 |

| DS2012 4K × 9 FIFO          | 89 |

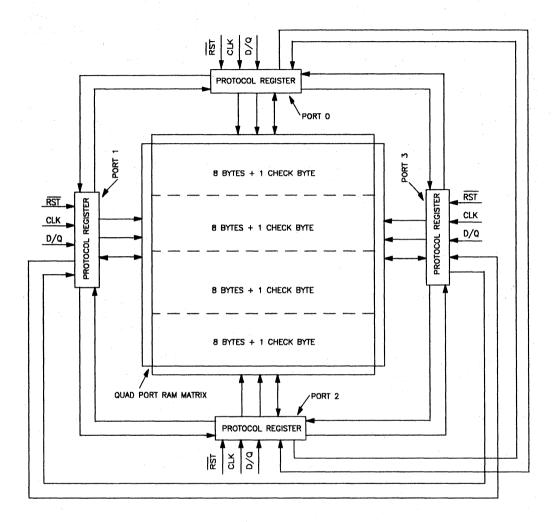

| DS2015 Quad Port Serial RAM | 90 |

#### Microcontroller

| DS5000 Soft Microcontroller     | 102 |

|---------------------------------|-----|

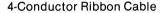

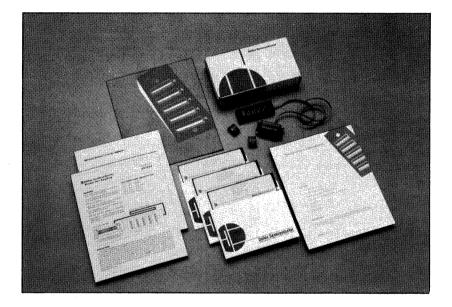

| DS5000K DS5000 Evaluation Kit   | 123 |

| DS5000DK DS5000 Development Kit | 128 |

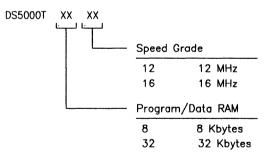

| DS5000T Soft Microcontroller    |     |

| with RTC                        | 129 |

#### Nonvolatile Static RAM

| DS1220AB/AD 16K Nonvolatile Static |     |

|------------------------------------|-----|

| RAM                                | 132 |

| DS1220Y 16K Nonvolatile Static RAM | 140 |

| DS1225AB/AD 64K Nonvolatile Static |     |

| RAM                                | 148 |

| DS1225Y 64K Nonvolatile Static     |     |

| RAM                                | 156 |

| DS1230Y/AB 256K Nonvolatile Static |     |

| RAM                                | 164 |

|                                    |     |

| DS1235Y/AB 256K Nonvolatile Static  |     |

|-------------------------------------|-----|

| RAM                                 | 172 |

| DS1245Y/AB 1024K Nonvolatile Static |     |

| RAM                                 | 180 |

# Intelligent Sockets

#### **Time Keeping**

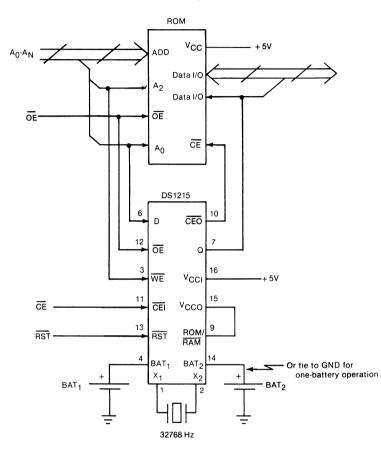

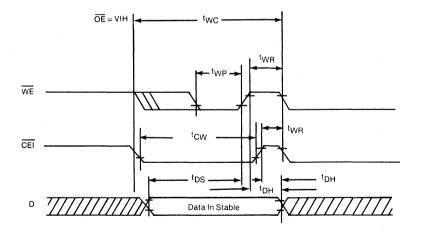

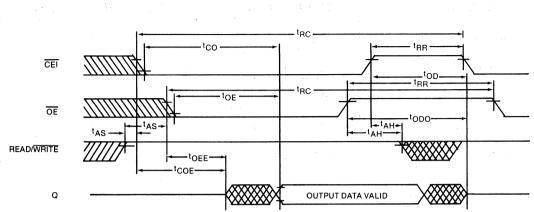

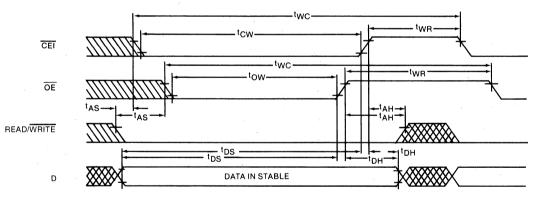

| DS1215 TimeChip                   | 240 |

|-----------------------------------|-----|

| DS1243Y 64K NVSRAM Plus RealTime  |     |

| Clock                             | 256 |

| DS1244Y 256K NVSRAM Plus          |     |

| RealTime Clock                    | 258 |

| DS1285/1285Q Real Time Clock Plus |     |

| RAM                               | 260 |

| DS1286 WatchDog Timekeeper        | 264 |

| DS1287 RealTime Clock Plus RAM    | 265 |

| DS1287A RealTime Clock Plus RAM   | 287 |

|                                   |     |

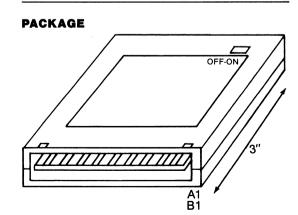

#### **User Insertable Memory**

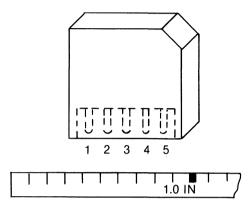

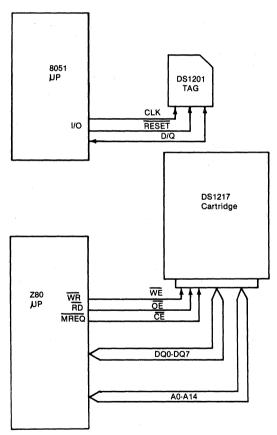

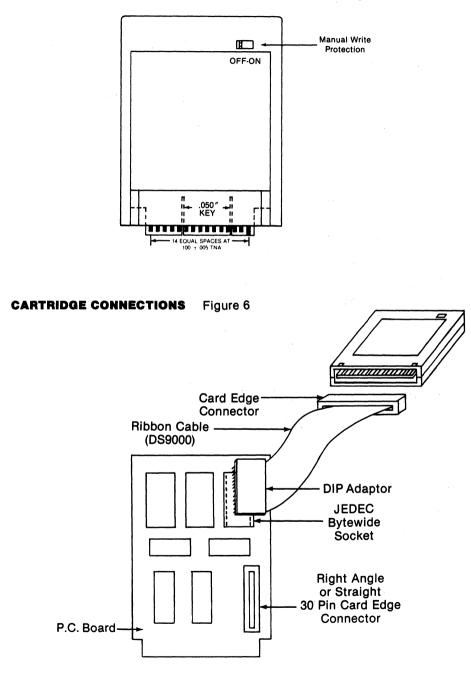

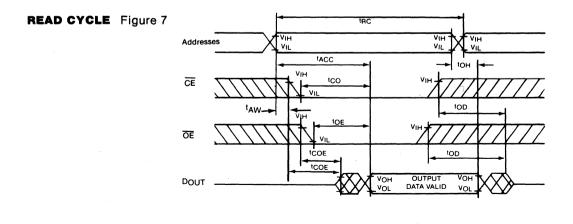

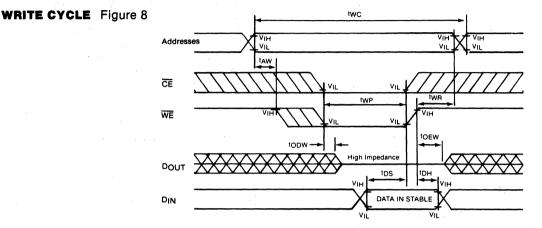

| DS1201 Electronic Tag          | 290 |

|--------------------------------|-----|

| DS1217A Nonvolatile Read/Write |     |

| Cartridge                      | 298 |

| DS1217I Nonvolatile Read/Write |     |

| Cartridge                      | 311 |

| DS1217M Nonvolatile Read/Write |     |

| Cartridge                      | 313 |

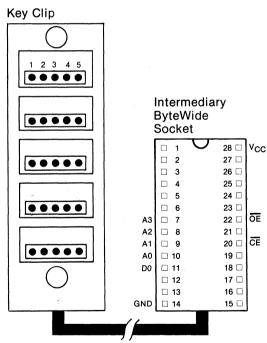

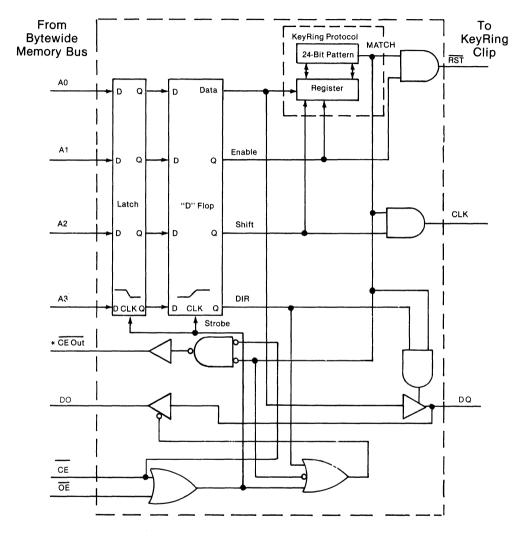

| DS1250 KeyRing                 | 324 |

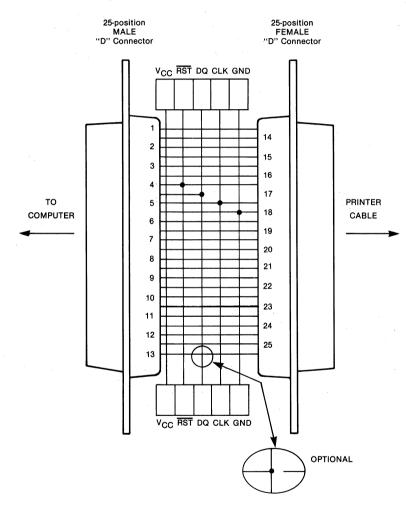

| DS6010 P.C. Port               | 332 |

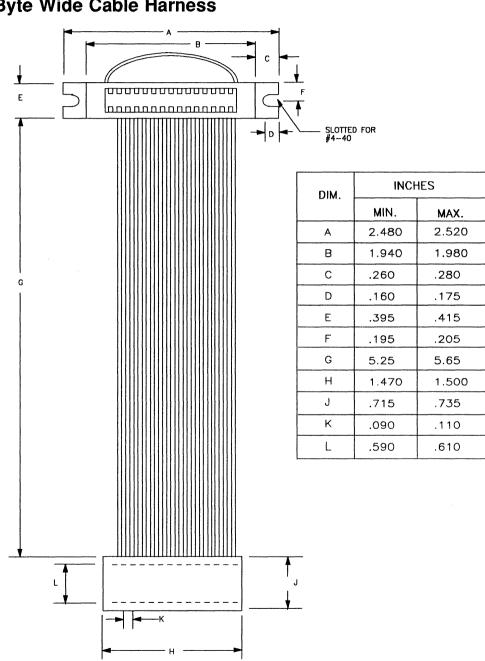

| DS9000 Bytewide Cable Harness  | 342 |

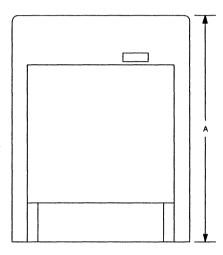

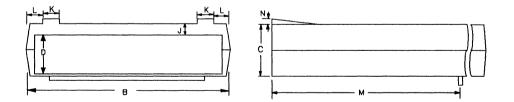

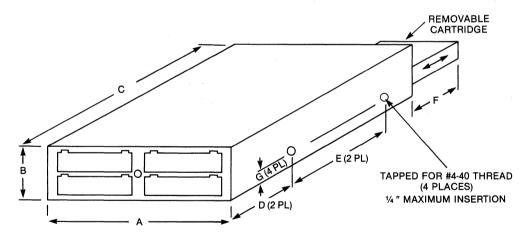

| DS9002 Cartridge Housing       | 344 |

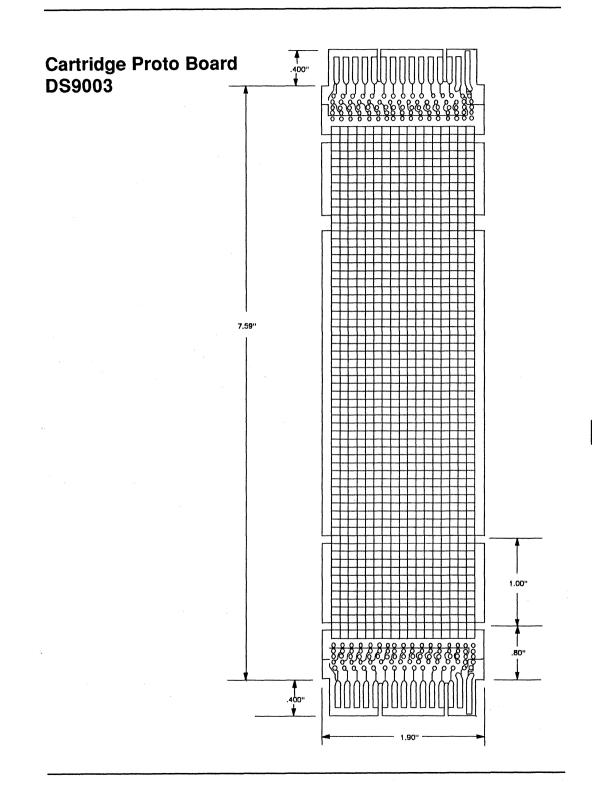

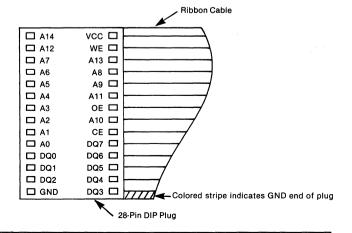

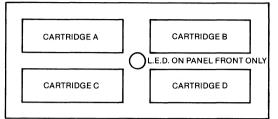

| DS9003 Cartridge Proto Board   | 346 |

| DS9020 Cartridge Clip          | 348 |

|                                |     |

# Security Products

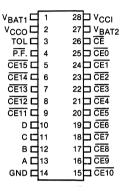

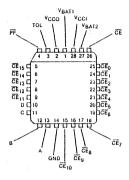

| DS1204U Electronic Key                     |  |

|--------------------------------------------|--|

| Integrated Battery Backup                  |  |

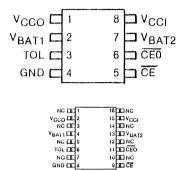

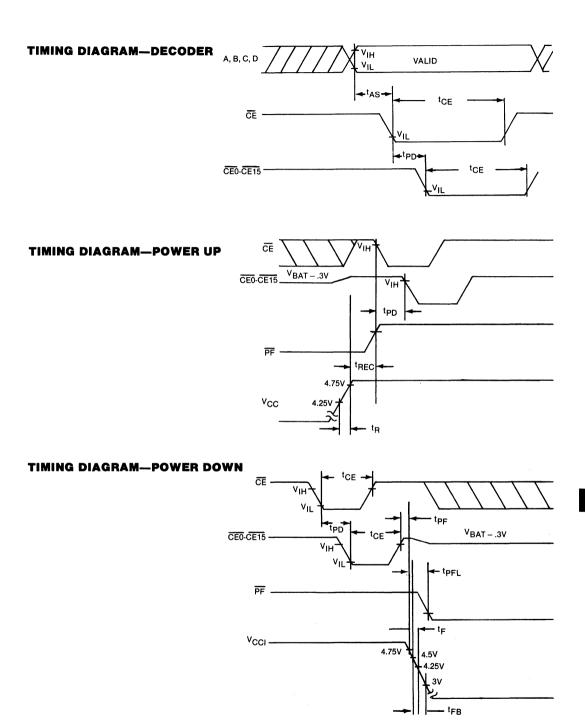

| DS1210 Nonvolatile Controller 402          |  |

| DS1211 × 8 Nonvolatile Controller/         |  |

| Decoder                                    |  |

| DS1212 $\times$ 16 Nonvolatile Controller/ |  |

| Decoder 414                                |  |

| DS1221 × 4 Nonvolatile Controller/         |  |

| Decoder                                    |  |

| DS1231 Power Monitor 436                   |  |

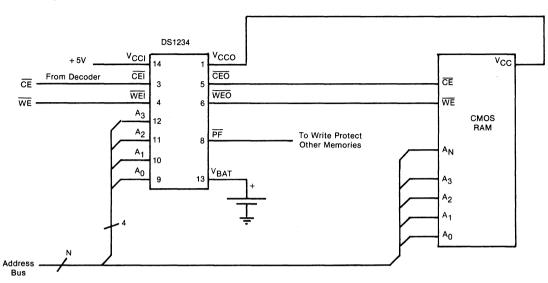

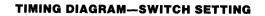

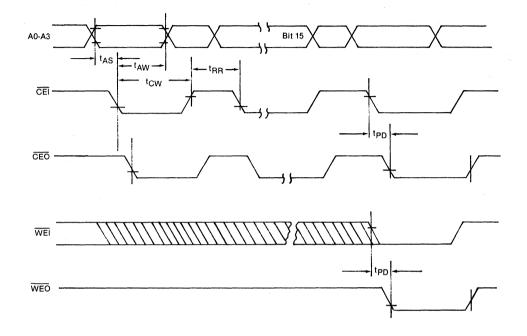

| DS1234 Conditional Nonvolatile             |  |

| Controller 448                             |  |

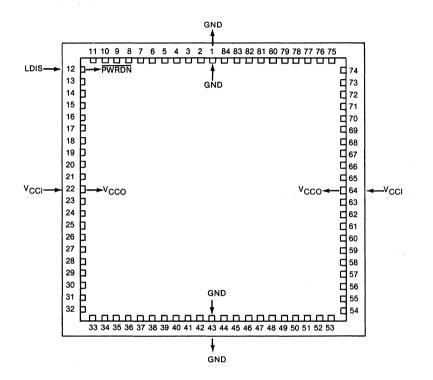

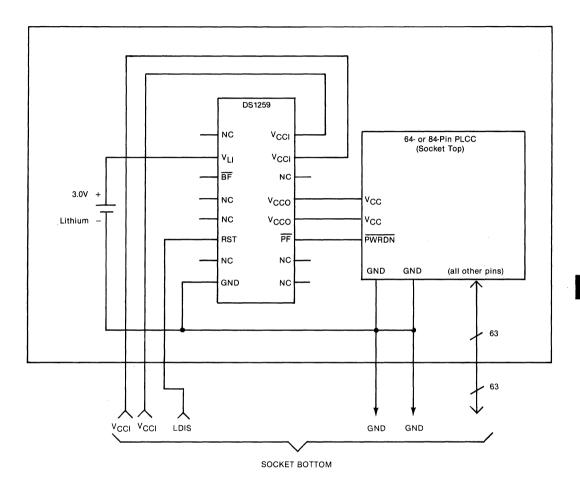

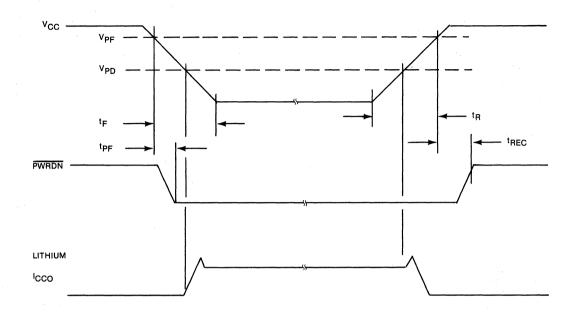

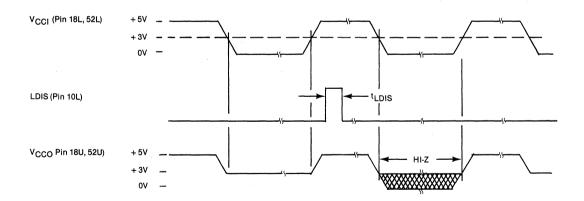

| DS1259 Battery Manager 460                 |  |

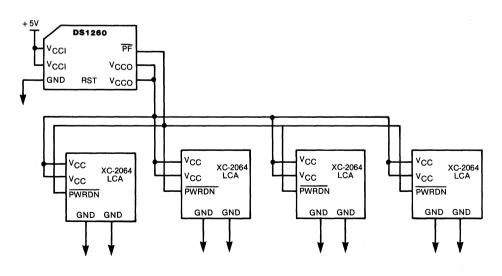

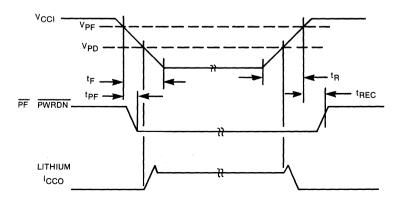

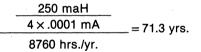

| DS1260 SmartBattery 468                    |  |

| System Extension                           |  |

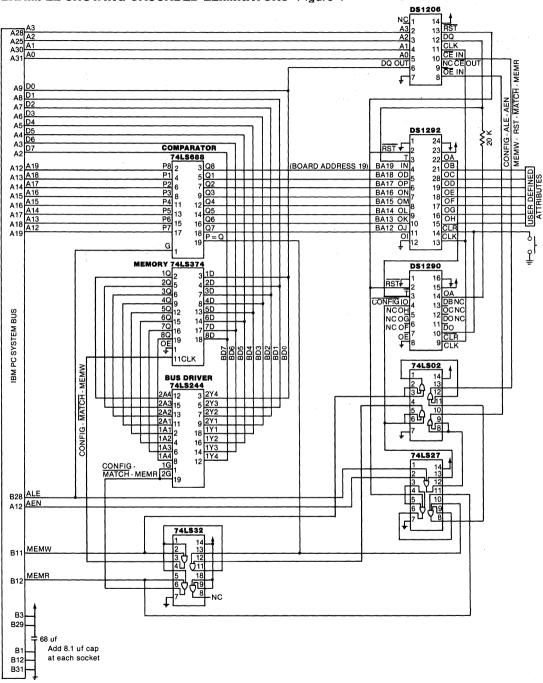

| DS1206 Phantom Interface 480               |  |

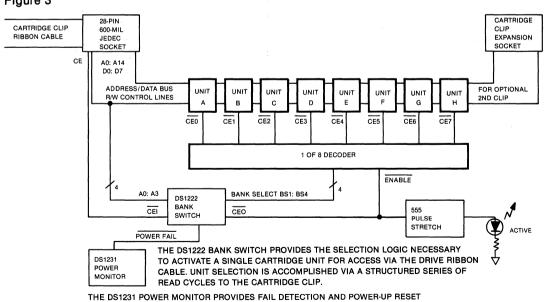

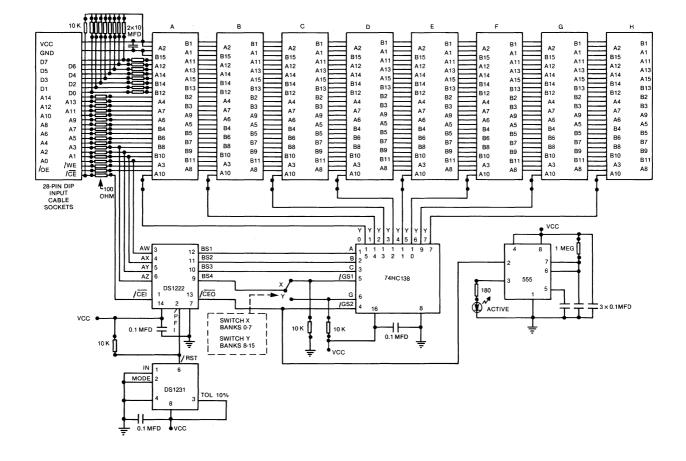

| DS1222 BankSwitch 490                      |  |

| DS1223 Electronic Configurator 499         |  |

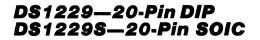

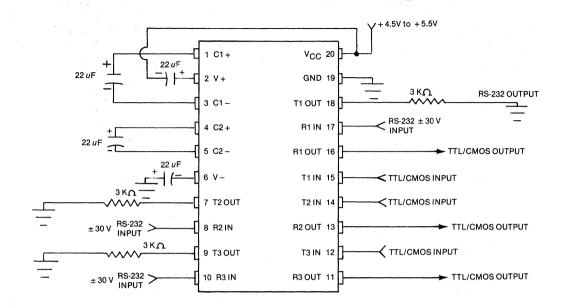

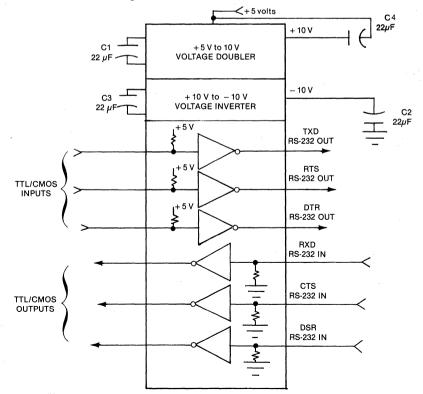

| DS232/DS1228 ± 5V Powered Dual             |  |

| RS-232 Transmitter/Receiver 510            |  |

| DS1229 + 5V Powered Triple RS-232          |  |

| Transmitter/Receiver 513                   |  |

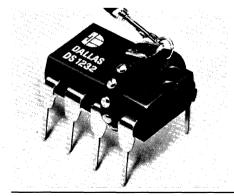

| DS1232 MicroMonitor                        |  |

| DS1290/DS1291 Eliminator 529               |  |

| DS1292/DS1293 Eliminator                   |  |

# SipStik<sup>™</sup> Products

| DS2209/DS2219 DRAM SipStik | 544 |

|----------------------------|-----|

| DS2217 SRAM SipStik        | 545 |

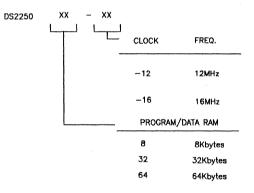

| DS2245 MODEM SipStik       | 553 |

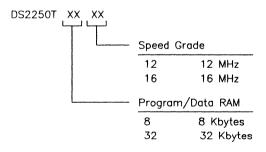

| DS2250 Micro SipStik       | 554 |

| DS2250T Micro SipStik      | 555 |

#### **Wireless Products**

| DS1203 Micro Power Receiver         | 558 |

|-------------------------------------|-----|

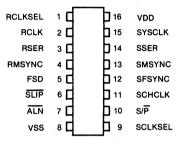

| DS1209 2 to 3 Wire Converter        | 559 |

| DS1280 Bytewide to Serial Converter | 560 |

| DS6065 E-Key                        | 561 |

| DS6068 RF Communicator              |     |

|                                     |     |

# Telecommunications\*

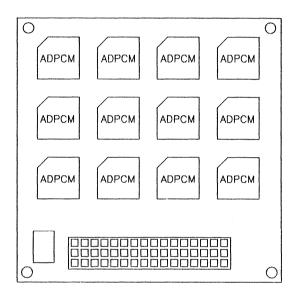

| DS2157/DS2158 ADPCM Array        | 564 |

|----------------------------------|-----|

| DS2167/DS2168 ADPCM Processor    | 565 |

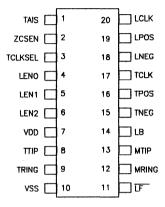

| DS2175 T1/CEPT Elastic Store     | 566 |

| DS2176 T1 Receive Buffer         | 567 |

| DS2180/DS2180A T1 Transceiver    | 568 |

| DS2180K T1 Design Kit            | 569 |

| DS2181 CEPT Transceiver          | 570 |

| DS2186 Transmit Line Interface   | 571 |

| DS2187 Receive Line Interface    | 572 |

| DS2190 T1 Network Interface Unit | 573 |

#### MODEM\*

| DS6101/DS6103 Modem                | 576 |

|------------------------------------|-----|

| DS6112 Data Access Arrangement     | 577 |

| DS6122 1200 BPS Modem              | 578 |

| DS6151/DS6153 Modem Evaluation Kit | 579 |

|                                    |     |

\*Complete Data Sheets available on request

# APPLICATION NOTES

| AN-1 Nonvolatile Static RAM          | 582   |

|--------------------------------------|-------|

| AN-2 User Insertable Nonvolatile RAM | 588   |

| AN-3 SmartSocket/SmartWatch          | 599   |

| AN-4 SmartSocket/SmartWatch          |       |

| Options                              | . 609 |

| AN-5 Integrated Battery Backup       | 613   |

| AN-8 Security System Locks Up        |       |

| Software                             | 624   |

| AN-9 System Configuration            |       |

| AN-10 Nonvolatile Configurable Logic |       |

| AN-12 KeyRing Options                |       |

| AN-13 P.C. Port Options              | 646   |

|                                      |       |

# **General Information**

Second Second Second Second

# **Product List**

| DS1000 5-Tap Silicon Delay Line 30    | DS1255 Printer Port KeyRing      | . 396 |

|---------------------------------------|----------------------------------|-------|

| DS1005 5-Tap Silicon Delay Line 38    | DS1255C Software Autho. Cookbook |       |

| DS1007 7-in-1 Silicon Delay Line 46   | DS1259 Battery Manager           |       |

| DS1010 10-Tap Silicon Delay Line 53   | DS1260 SmartBattery              | . 468 |

| DS1013 3-in-1 Silicon Delay Line 60   | DS1264/DS1265 LCA SmartSocket    |       |

| DS1015 Data Separator                 | DS1280 Bytewide Serial Converter | . 560 |

| DS1201 Electronic Tag                 | DS1285 Real Time Clock Plus RAM  |       |

| DS1203 Micro Power Receiver 558       | DS1286 WatchDog TimeKeeper       | . 264 |

| DS1204U Electronic Key                | DS1287 Real Time Clock Plus RAM  | . 265 |

| DS1206 Phantom Interface              | DS1287A Real Time Clock Plus RAM |       |

| DS1207 TimeKey                        | DS1290/DS1291 Eliminator         | . 529 |

| DS1209 2 to 3 Wire Converter 559      | DS1292/DS1293 Eliminator         |       |

| DS1210 Nonvolatile Controller 402     | DS2009 512 × 9 FIFO              | . 70  |

| DS1211 × 8 NV Controller Decoder 411  | DS2010 1K × 9 FIFO               |       |

| DS1212 × 16 NV Controller Decoder 414 | DS2011 2K × 9 FIFO               |       |

| DS1213 SmartSocket 190                | DS2012 4K × 9 FIFO               |       |

| DS1213C SmartSocket 197               | DS2015 Quad Port Serial RAM      |       |

| DS1213D SmartSocket 198               | DS2157/DS2158 ADPCM Array        | . 564 |

| DS1215 Time Chip 240                  | DS2167/DS2168 ADPCM Processor    |       |

| DS1216 SmartWatch/RAM                 | DS2175 T1/CEPT Elastic Store     |       |

| DS1216C SmartWatch/RAM 211            | DS2176 T1 Receiver Buffer        |       |

| DS1216D SmartWatch/RAM 212            | DS2180/DS2180A T1 Transceiver    |       |

| DS1216E SmartWatch/ROM                | DS2180K T1 Design Kit            | . 569 |

| DS1216F SmartWatch/ROM 225            | DS2181 CEPT Transceiver          | . 570 |

| DS1217A NV Read/Write Cartridge 298   | DS2186 Transmit Line Interface   |       |

| DS1217I NV Read/Write Cartridge 311   | DS2187 Receive Line Interface    | . 572 |

| DS1217M NV Read/Write Cartridge 313   | DS2190 T1 Network Interface Unit |       |

| DS1220AB/AD 16K NV Static RAM 132     | DS2209/DS2219 DRAM SipStik       | . 544 |

| DS1220Y 16K NV Static RAM 140         | DS2217 SRAM SipStik              |       |

| DS1221 × 4 NV Controller Decoder 423  | DS2245 MODEM SipStik             | . 553 |

| DS1222 BankSwitch 490                 | DS2250 Micro SipStik             | . 554 |

| DS1223 Electronic Configurator 499    | DS2250T Micro SikStik            | . 555 |

| DS1225AB/AD 64K NV Static RAM 148     | DS5000 Soft Microcontroller      |       |

| DS1225Y 64K NV Static RAM 156         | DS5000K DS5000 Evaluation Kit    | . 123 |

| DS232/DS1228 Dual RS-232 TX/RX 510    | DS5000DK DS5000 Development Kit  | . 128 |

| DS1229 Triple RS-232 TX/RX 513        | DS5000T Soft Micro with RTC      | . 129 |

| DS1230Y/AB 256K NV Static RAM 164     | DS6010 P.C. Port                 | . 332 |

| DS1231 Power Monitor                  | DS6065 E-Key                     | . 561 |

| DS1232 MicroMonitor                   | DS6068 RF Communicator           | . 562 |

| DS1234 Conditional NV Controller 448  | DS6101/DS6103 MODEM              | 576   |

| DS1235Y/AB 256K NV Static RAM 172     | DS6112 Data Access Arrangement   | 577   |

| DS1243Y 64K NVSRAM Plus RTC 256       | DS6122 1200 BPS MODEM            | 578   |

| DS1244Y 256K NVSRAM Plus RTC 258      | DS6151/DS6153 MODEM Eval. Kit    | 579   |

| DS1245Y/AB 1024K NV Static RAM 180    | DS9000 Bytewide Cable Harness    |       |

| DS1250 KeyRing 324                    | DS9002 Cartridge Housing         |       |

| DS1253 Printer Port KeyRing           | DS9003 Cartridge Proto Board     | 346   |

| DS1253K Software Autho, Kit           | DS9020 Cartridge Clip            |       |

1

# **Corporate Fact Sheet**

Dallas Semiconductor designs, manufactures and markets CMOS integrated circuits using special Late Definition technology. Late Definition permits the exact definition of a product to be postponed until end use, thereby increasing flexibility.

#### PRODUCTS

Founded February 1, 1984, Dallas Semiconductor has a multi-product strategy to serve the needs of the computer and communications industry. Our optimism stems from the ability to sell "Soft Silicon" which can be readily tailored to solve the specific problems of our customers. Soft silicon results from the Late Definition technologies of lithium, laser, and implant. Lithium postpones definition until end use, thereby making the chip adaptive in the system. Laser postpones definition until just before the chip is placed in the package, and implant postpones definition until the last wafer process step.

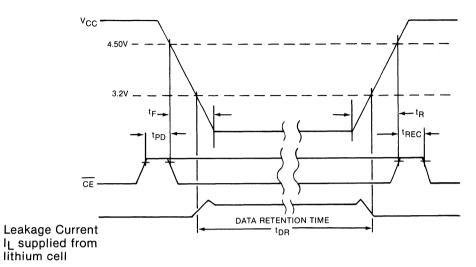

### LITHIUM

Advances in CMOS circuitry have reduced power requirements to the point that a chip, using appropriate circuitry, can be packaged with a miniature lithium energy source which will last the useful life of the equipment. This allows Dallas Semiconductor to make chips which don't forget. Our initial product offerings exploited this capability to make the much sought-after nonvolatile RAM. In November 1984 we began shipping 16K, 64K Nonvolatile SRAMs.

Keeping track of human time has not been an easy task for computers until our July 1985 announcement of the DS1216 SmartWatch. It precisely keeps calendar time down to the hundredth of a second, replacing what heretofore consumed a whole printed circuit board full of electronics. A lithium cell provides power for life.

The adaptive nature of CMOS/Lithium products is made evident by the April 1987 introduction of the DS5000 Soft Microcontroller. Designed with change in mind, it offers unprecedented software adaptability and crashproof operation. The capabilities of the Soft Microcontroller take it beyond mere update change and into the realm of learning. The DS5000 can capture a large amount of data in real time and remember it indefinitely. With the proper application software, the microcontroller can improve its performance based on that cumulative knowledge.

#### LASER

The laser creates uniqueness on a chip at low cost. A sub-micron positioning laser and formidable control software developed at Dallas can engrave individual chips with digital patterns making each one different. These afterthe-fact changes to completed circuits give our laser-based products a competitive edge.

The first product that demonstrated our special laser technology was an extremely accurate time base, commonly referred to as a delay line. Before the August 1985 announcement date, it had only been possible to build such devices using a dozen components in a hybrid assembly. The DS1000 Silicon Delay Line series is a direct replacement for hybrid delay lines which are widely used in conjunction with DRAMs and magnetic disks.

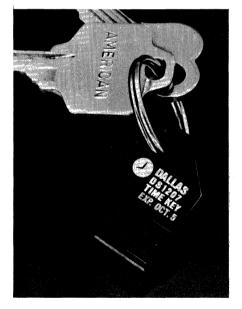

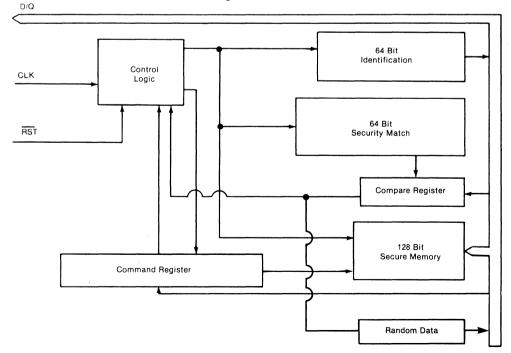

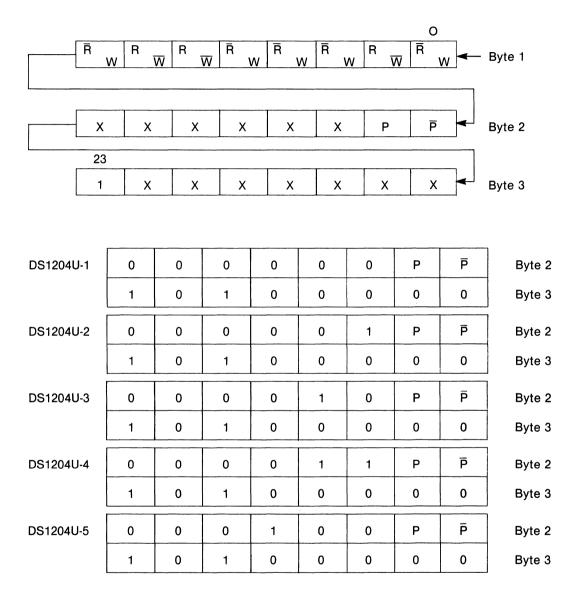

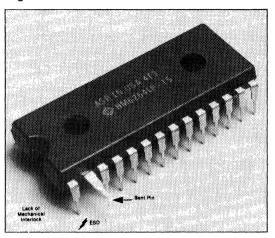

Other products use the laser to protect sensitive information and intellectual property by creating a powerful security mechanism in micro chips. The DS1204 Electronic Key is an example of a product which benefits from the laser in this regard. Exclusive blank Keys are defined by laser for each customer, adding to the overall security mechanism. Additional products are on the drawing board whereby the laser tailors the option content of the chip for a particular customer. In short, the laser lets Dallas Semiconductor define each chip uniquely after it is already operational.

#### IMPLANT

Nearly-finished wafers can be defined to meet exact customer requirements in a matter of days with high energy ion implant technology. A number of products will be offered with an "Express Delivery Service."

Difficult system problems have been solved by relying on these special technologies, experience, and creativity, to offer our customers a more complete solution than the chip alone can provide. Often this requires a greater emphasis on packaging than traditional semiconductor producers have been accustomed. Fifty-one base products were put into production prior to January 1988, unified by our own CMOS technology.

#### **MANUFACTURING AND FACILITIES**

Dallas Semiconductor manufactures products at a 65,000-square-foot facility, which it owns, located at the company's headquarters in north Dallas. This location includes an advanced Class One wafer fabrication facility completed in 1987. Six-inch wafers are processed with circuits utilizing sub-micron geometries. Automated modular process technology provides substantial flexibility in the manufacturing process and significantly reduces the number of people required for operation, thereby decreasing manufacturing costs. The company's wafer fabrication facility contains a 10,000-square-foot cleanroom. The sensitivity of the manufacturing process to particulates and other contaminants requires a highly controlled, clean environment. All products are shipped from Dallas after final quality assurance testing.

#### **MARKETING AND SALES**

Dallas Semiconductor sells its products to a large and diverse customer base of both mature and emerging OEMs in the computer, telecommunications, instrumentation, and factory automation markets. The Company coordinates its selling activity from its Dallas, Texas headquarters. Five area sales offices are staffed in Marlton. New Jersev: Cupertino. California; Los Angeles, California; Carmel, Indiana; and Birmingham, England. The Company's five area sales managers call on OEM accounts and coordinate the activities of 45 sales representative offices in North America and 22 in European countries and Asia. Dallas Semiconductor also markets its products in North America through a national stocking distributor and through ten regional distributors.

# North American Sales Offices

Northern California Cupertino, CA (408) 973-7850

#### Southern California Newport Beach, CA (714) 646-7219

Indiana Carmel, IN (317) 844-5044

#### New Jersey Mariton, NJ

(609) 667-7755

#### **Texas** Dallas, TX (214) 450-0400

# European Sales Office

West Midlands, UK 021-745-8252

# International Distributors

Australia Alfatron Pty, Ltd. Victoria (03) 758-9000

#### **Austria** Hitronik Vienna (0222) 824199

Belgium BETEA Brussels/Benelux (02) 736-8050

# France

REA Levallois Perret 758.11.11

Holland Alcom Electronics Rotterdam 010 451 95 33 Tekelec Airtronic Paris (1) 534.75.92

Hong Kong Cet, Ltd. (5) 200922

**India** Malhar Corp. Bangalore 812-564464

Northern Ireland Bloomer Electronics Ltd. Craigavon Co. Armagh 0762 339818

Israel STG International Tel Aviv (3) 248231

**Italy** Comprel, S.P.A. Milan (02) 612-0641

Tekelec Airtronic Mameli (02) 738-0641

**Japan** Systems Marketing, Inc. Tokyo 03-254-2751

Microtek Inc. Tokyo 03-371-1811

**Malaysia** Dynamar Int'l, Ltd. Singapore 7476188

**Portugal** Digicontrole Lisbon 292.39.24

Scandinavia Integrerad Elektronik Komponenter AB Bromma 08-80 4685 Sweden Commit Electronics AB Taby 08 792 3650

**Singapore** Dynamar Int'l, Ltd. 65-7476188

South Korea Vine Overseas Trading Seoul (02) 266-1663

**Spain** Comelta, S.A. Madrid (01) 754-3001

Switzerland Kontron Electronic AG Zurich 01/435 4111

**Taiwan** Landcol Enterprises, Ltd. Taipei (02) 709-3515

United Kingdom Joseph Electronics, Ltd. West Midlands 021-643-6999

Ambar Cascom Ltd. Bucks 296-434-141

Dialogue Distribution Ltd. Camberly, Surrey 0276-682001

West Germany Atlantik Elektronik Gmbh. Martinsried/Munich (089) 8 57 2086

Astek Elektronik Kaltenkirchen 4191-8711

Kontron Halbleiter GmbH Munich 319 01-377

# **North American Sales Representatives**

#### Alabama

Glen White and Associates Huntsville, AL (205) 882-6751

### California

l<sup>2</sup>, Inc. Santa Clara, CA (408) 988-3400

S C Cubed Tustin, CA (714) 731-9206

Thousand Oaks, CA (805) 496-7307

Harvey King, Inc. San Diego, CA (619) 587-9300

#### Canada

Davetek Marketing Vancouver, BC (604) 430-3680

Electro-Source, Inc. Rexdale, Ontario (416) 675-4490

Nepean, Ontario (613) 726-1452

Pointe Claire, Quebec (514) 694-0404

Colorado

Waugaman Associates Wheat Ridge, CO (303) 423-1020

**Connecticut** Technology Sales, Inc. Yalesville, CT (203) 269-8853

#### Florida

E.I.R., Inc. Maitland, FL (305) 660-9600

Georgia

Glen White and Associates Norcross, GA (404) 441-1447

### Illinois

Sumer, Inc. Rolling Meadows, IL (312) 991-8500

#### Indiana

Electronic Sales & Eng. Indianapolis, IN (317) 849-4260

#### lowa

Cahill, Schmitz and Howe, Inc. Cedar Rapids, IA (319) 377-8219

Kansas Technical Sales Associates Olathe, KS (913) 829-2800

Maryland Arbotek Associates Towson, MD (301) 825-0775

Massachusetts Technology Sales, Inc. Waltham, MA (617) 890-5700

Michigan Giesting & Associates Farmington Hills, MI (313) 478-8106

Minnesota Cahill, Schmitz & Cahill, Inc. St. Paul, MN (612) 646-7217

**Mississippi** Glen White and Associates Jackson, MS (601) 856-5411

**Missouri** Technical Sales Associates St. Louis, MO (314) 521-2044

New Jersey Sunday O'Brien, Inc. Haddonfield, NJ (609) 429-4013

New Mexico Reptronix, Ltd. Albuquerque, NM (505) 292-1718

#### **New York**

Advanced Components Corp., Inc. Cicero, NY (315) 699-2671

S-J Associates Jamaica, NY (718) 291-3232

### **North Carolina**

Glen White and Associates Raleigh, NC (919) 848-1931

H & A Sales Raleigh, NC (919) 846-0082

#### Ohio

Giesting & Associates Cincinnati, OH (513) 385-1105

Giesting & Associates Cleveland, OH (216) 261-9705

Giesting & Associates Dayton, OH (513) 433-5832

**Oklahoma** West Associates Tulsa, OK (918) 665-3465

**Oregon** Western Technical Sales Beaverton, OR (503) 644-8860

**Pennsylvania** Giesting & Associates Pittsburgh, PA (412) 963-0727

Puerto Rico Technology Sales (809) 892-4745

**Tennessee** Glen White and Associates Gray, TN (615) 477-8850

#### Texas

West Associates, Inc. Austin, TX (512) 339-6886

West Associates, Inc. Dallas, TX (214) 680-2800

West Associates, Inc. Houston, TX (713) 621-5983

#### Utah

Waugaman Associates Salt Lake City, UT (801) 261-0802

#### Washington State

Western Technical Sales Bellevue, WA (206) 641-3900

Western Technical Sales Spokane, WA (509) 922-7600

#### Wisconsin

Sumer, Inc. Brookfield, WI (414) 784-6641

# **North American Distributors**

Added Value Electronic Distribution Inc. (AVED) California Tustin, CA (714) 259-8258

### **Advent Electronics**

Iowa Cedar Rapids, IA (319) 363-0221

Michigan Farmington Hills, MI (313) 477-1650

#### **Almac Electronics**

**Oregon** Beaverton, OR (503) 629-8090

#### Washington

Bellevue, WA (800) 426-1410 Spokane, WA

(800) 426-1410

#### **Bell Industries**

Illinois Urbana, IL (217) 328-1077

Indiana Indianapolis, IN (317) 875-8200

Ft. Wayne, IN (219) 423-3422

#### Michigan

Ann Arbor, MI (313) 971-9093

#### Ohio

Dayton, OH (513) 435-8660

#### **Future Electronics**

**Canada** Calgary, Alberta (403) 235-5325

Edmonton, Alberta (403) 486-0974

Pointe Claire, Quebec (514) 694-7710

Ottawa, Ontario (613) 820-8313

Downsview, Ontario (416) 638-4771

Vancouver, BC (604) 294-1166

#### **Hall-Mark Electronics**

Alabama Huntsville, AL (205) 837-8700

**Arizona** Phoenix, AZ (602) 437-1200

California Canoga Park, CA (818) 716-7300

Citrus Heights, CA (916) 722-8600

Torrance, CA (213) 643-9101

San Diego, CA (619) 268-1201

San Jose, CA (408) 432-0900

Tustin, CA (714) 669-4700

Colorado Englewood, CO (303) 790-1662

**Connecticut** Wallingford, CT (203) 269-0100

Florida Clearwater, FL (813) 530-4543

Orlando, FL (305) 855-4020

Pompano Beach, FL (305) 971-9280

**Georgia** Norcross, GA (404) 447-8000

Illinois Woodale, IL (312) 860-3800 Indiana

Indianapolis, IN (317) 872-8875

#### Kansas Lenexa, KS (913) 888-4747

Maryland Columbia, MD (301) 988-9800

Massachusetts Billerica, MA (617) 935-9777

Minnesota Eden Plains, MN (612) 941-2600

**Missouri** Earth City, MO (314) 291-5350

North Carolina Raleigh, NC (919) 872-0712

New Jersey Fairfield, NJ (201) 575-4415

Mt. Laurel, NJ (609) 235-1900

New York Ronkonkoma, NY (516) 737-0600

Ohio Solon, OH (216) 349-4632

Worthington, OH (614) 888-3313

**Oklahoma** Tulsa, OK (918) 665-3200

**Texas** Austin, TX (512) 258-8848

Dallas, TX (214) 553-4300 Houston, TX (713) 781-6100 Utah Murray, UT (801) 972-1008

Wisconsin New Berlin, WI (414) 797-7844

#### Industrial Components

Minnesota Minneapolis, MN (612) 831-2666

#### Insight Electronics

**Arizona** Tempe, AZ (602) 829-1800

**California** San Diego, CA (619) 587-0471

Costa Mesa, CA (714) 556-6890

Augora Hills, CA (818) 707-2100

#### **Milgray Electronics**

Connecticut Orange, CT (203) 795-0711

New Jersey Mariton, NJ (609) 983-5010

Florida Winter Park, FL (305) 647-5747

**Georgia** Atlanta, GA (404) 393-9666

Illinois Bensenville, IL (312) 350-0490

Kansas Overland Park, KS (913) 236-8800

Maryland Columbia, MD (301) 621-8169 New England Wilmington, MA (617) 657-5900

New York Farmingdale, NY (516) 420-9800

Rochester, NY (716) 235-0830

**Ohio** Cleveland, OH (216) 447-1520

**Texas** Dallas, TX (214) 248-1603

**Canada** Willowdale, Ontario

#### **Quality Components**

Alabama Huntsville, AL (205) 830-1881

**Georgia** Norcross, GA (404) 449-9508

North Carolina Raleigh, NC (919) 876-7767

**Oklahoma** Tulsa, OK (918) 664-8812

**Texas** Addison, TX (214) 733-4300

Austin, TX (512) 835-0220

Sugarland, TX (713) 240-2255

#### Western Microtechnology

Arizona Scottsdale, AZ (602) 948-4240

**California** Cupertino, CA (408) 725-1660

#### Oregon

Beaverton, OR (503) 629-2082

# Washington

Redmond, WA (206) 881-6737

### Wyle Laboratories

#### Arizona

Phoenix, AZ (602) 866-2888

#### California

Calabasas, CA (818) 880-9000

Irvine, CA (714) 863-9953

Rancho Cordova, CA (916) 638-5282

San Diego, CA (619) 565-9171

Santa Clara, CA (408) 727-2500

#### Colorado

Thornton, CO (303) 457-9953

#### Oregon

Hillsboro, OR (503) 640-6000

#### Texas

Austin, TX (512) 834-9957

Dallas, TX (214) 235-9953

Houston, TX (713) 879-9953

### Utah

Salt Lake City, UT (801) 974-9953

### Washington

Bellevue, WA (206) 453-8300

# **PRODUCT OVERVIEW**

### **Silicon Timed Circuits**

Electronic systems require exact timing to control the transmission of data between their component parts. Timing requirements vary across systems. Historically, systems designers have not been able to use semiconductors as timing references because of their lack of precision: they consequently achieved the required accuracy by using, in combination, quartz crystals and hybrid passive components. known as delay lines. All silicon delay lines offer single chip reliability, economy and significantly greater precision due to their laser-defined specifications. Direct laser writing provides precise accuracy and, because the products are defined in the final stage of manufacturing, a broad product mix is available without losing the economic benefits of standard integrated circuit production. Customers are provided maximum flexibility, as well as the option of purchasing tailor-made products at the approximate cost of standard, off-the-shelf solutions. These all silicon products can be retrofitted into existing systems which otherwise utilize hybrid approaches as well as designed into new systems.

DS10005 TAP Delay Line DS101010 TAP Delay Line DS10133 in 1 Delay Line DS10077 in 1 Delay Line

### **Multiport Memory**

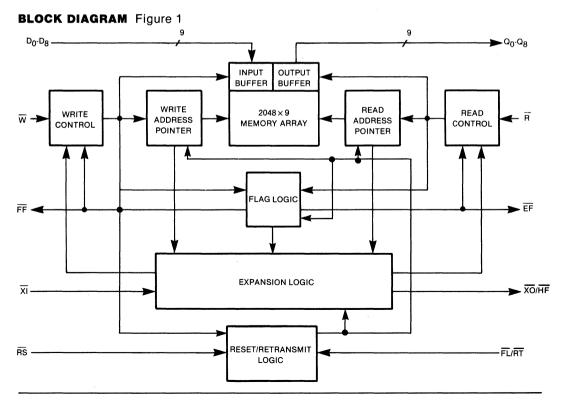

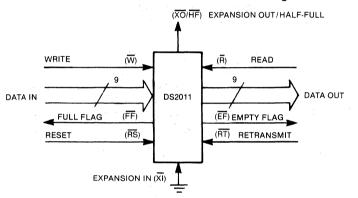

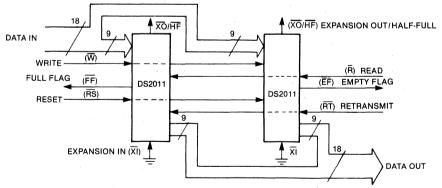

The existence of many different data transmission rates and standards has created a problem in transporting data among different systems. A receiving system may be too slow to keep up with data sent from another system. First In, First Out (FIFO) memories are capable of providing the necessary elasticity between different data rates.

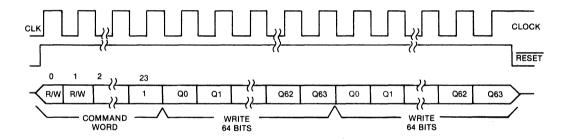

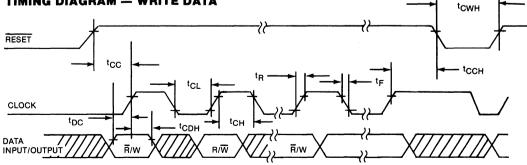

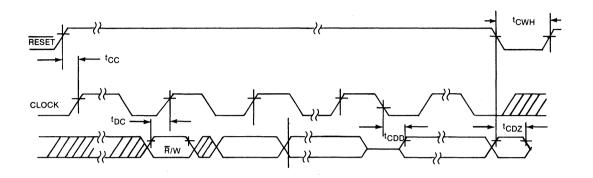

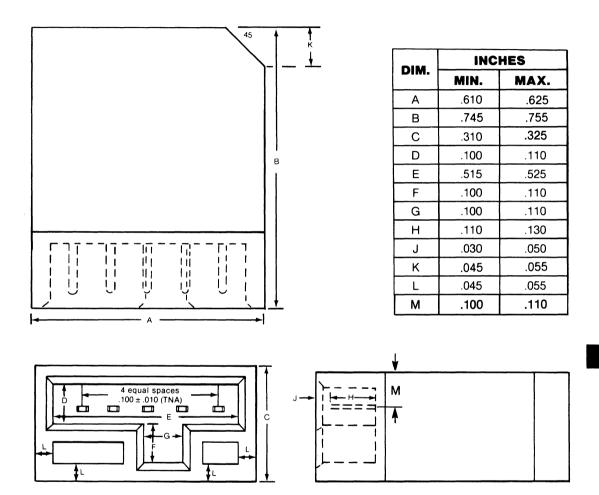

DS2009 512 x 9 FIFO DS2010 1K x 9 FIFO DS2011 2K x 9 FIFO DS2012 4K x 9 FIFO DS2015 4 x 64 Quadport Serial RAM

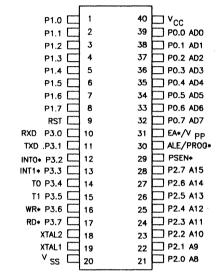

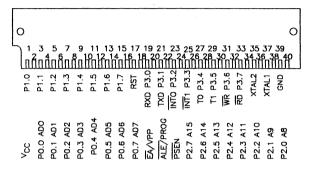

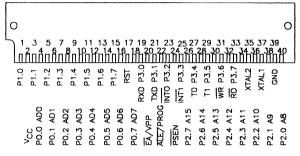

### Microcontroller

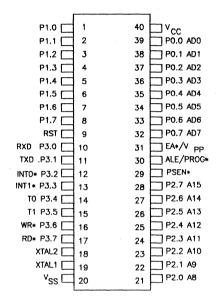

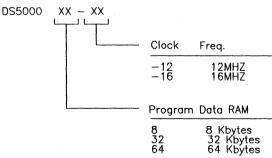

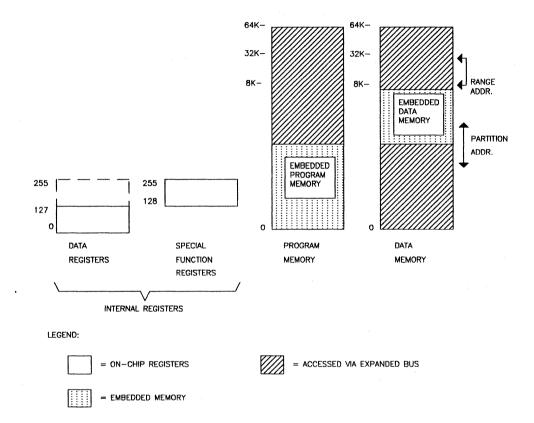

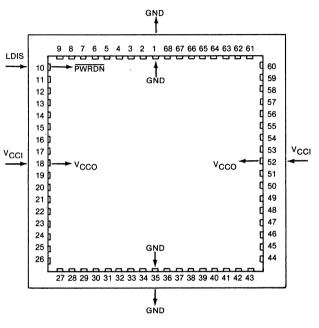

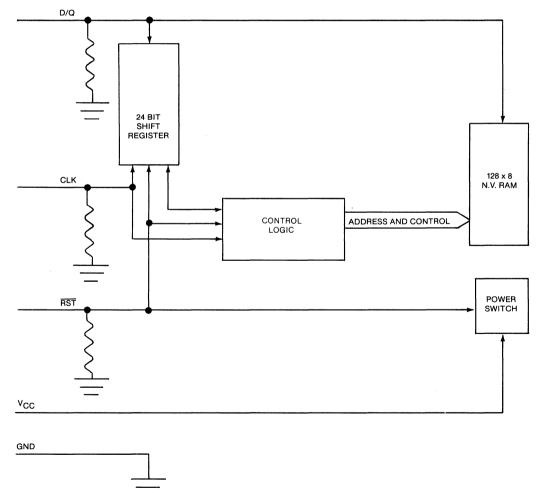

The DS5000 Soft Microcontroller stavs up-to-date because it was designed for change. Unlike rigid ROM or EPROM based microcontrollers, all of the Soft Microcontroller memory is high performance, read/write, and nonvolatile for more than ten years. The DS5000 is equipped with 32K bytes of nonvolatile SRAM which can be dynamically partitioned to fit program and data storage requirements of a particular task. As a result of sophisticated crashproofing circuitry, processing of a task can resume after a power outage. A built-in encrypter prevents unauthorized access to resident application software. The pinout and instruction set match the industry standard 8051 microcontroller. Additional information is available in a special publication called the Soft Microcontroller User Guide. The DS5000K evaluation kit includes a sample DS5000, documentation. in-system loader hardware and DOS compatible software for use with a personal computer.

# **Nonvolatile SRAM**

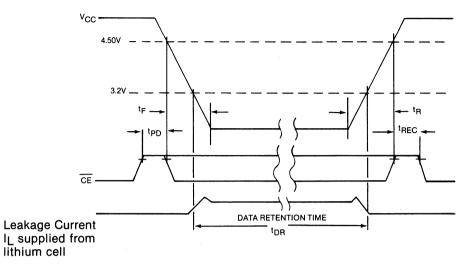

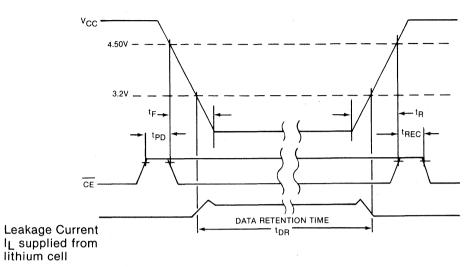

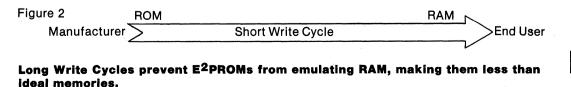

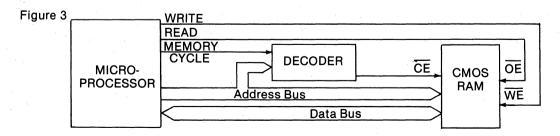

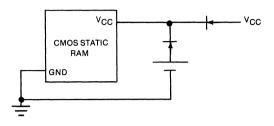

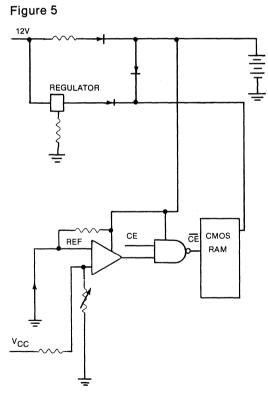

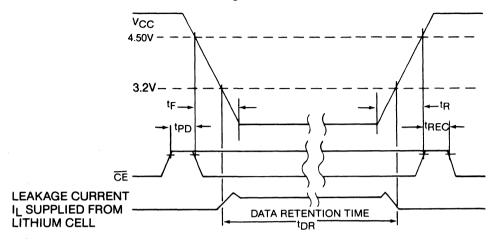

SRAMS have always had the undesirable characteristic of data loss when power is disrupted. Dallas Semiconductor has combined its knowledge of ultra low power CMOS SRAMs with improvements in long life embedded lithium power sources to develop a family of Nonvolatile SRAMs. Nonvolatile SRAMs integrate a lithium power source and intelligent control circuitry to retain data even in the absence of system power. The control circuit, by monitoring the level of system voltage available to the memory at all times, switches to the lithium power source when necessary, and also protects the memory contents against inadvertent change during system power fluctuatuions. A lithium power source provides backup power for more than 10 years in the absence of system power. Nonvolatile SRAMs are packaged to fit into existing sockets and can replace other widely used memory devices. These products perform better in many applications than EEPROMs, EPROMs, or shadow RAMs because they provide unlimited data write cycles, safeguard against corrupted data and write data in as fast as 70 ns. DS1220 2K x 8 24 pin Nonvolatile SRAM DS12258K x 828 pin Nonvolatile SRAM DS1230 32K x 8 28 pin Nonvolatile SRAM

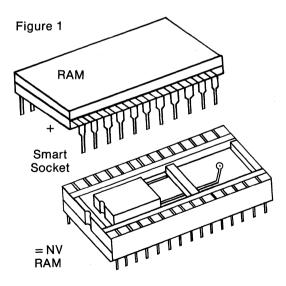

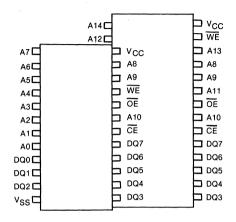

# Intelligent Sockets

Often, after a design is complete, the manufacturer may desire to enhance functionality because of increased competition from newer products. The equipment manufacturer is forced either to avoid adding features or design a new system. Dallas Semiconductor has incorporated active electronics in connectors which can be plugged into a system and add capabilities without requiring substantive changes in the existing system. For example, many systems manufacturers desire the capability to make RAMs in existing systems nonvolatile. In this instance, they can unplug a memory circuit in a system currently in use, plug the SmartSocket into that space, and plug the memory circuit into the SmartSocket. Another example is a requirement in many existing systems to monitor and record time of day. The SmartWatch plugs into existing systems and keeps time of day to hundredths of a second while also making memory circuits nonvolatile.

DS1213 SmartSocket - makes CMOS RAM nonvolatile

DS1216 SmartWatch - adds the ability to time stamp and date events

DS1264 LCA SmartSocket - maintains logic in the absence of power

# TimeKeeping

Systems benefit by knowing the time-of-day, but the use of this feature has been limited by its expense and high component count. A self-contained lithium energy source in conjunction with a silicon chip and quartz form a permanently **powered clock/calendar** within a single component. The DS1287 Real Time replaces 20 parts used in the IBM AT and PS/2 compatible computers including an MC146818 Real Time Clock plus RAM.

DS1215 TimeChip DS1287 Real Time DS1286 WatchDog

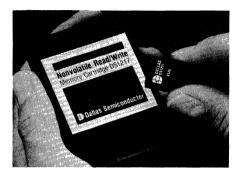

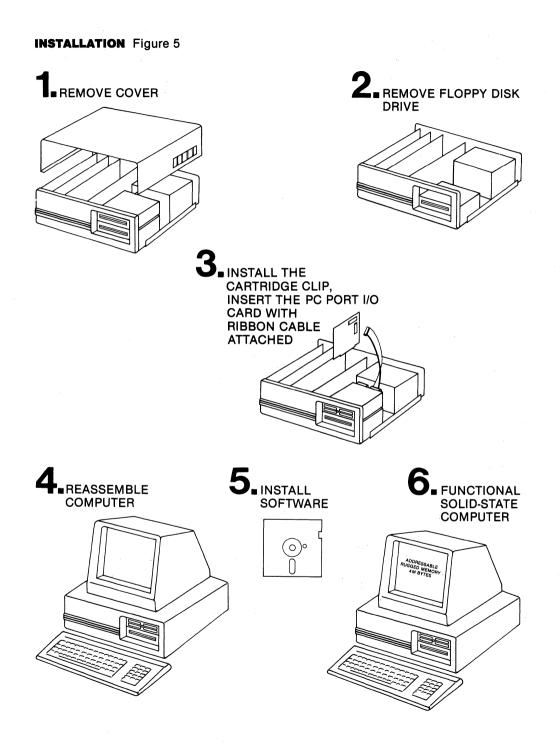

### **User Insertable Memory**

Manufacturers of equipment often wish to facilitate user configuration of their standard products. In many instances, user insertable solid state memories offer distinct advantages over alternative media, such as magnetic tape or disk. Such memories, however, demand specialized packaging capable of withstanding harsher environmental conditions than those normally encountered by semiconductor memory circuits. A family of Nonvolatile SRAMs has been specifically developed to address this application sector. These products range in density from 1024 bits to 32,000,000 bits, the largest of which replaces rotating memory subsystems in certain personal computer systems.

DS1201 1K bit Electronic Tag DS1217A up to 256K bit Nonvolatile Read/Write Cartridge DS1217M up to 4M bit Nonvolatile Read/Write Cartridge DS6010 P.C. Port DS9020 Cartridge Clip

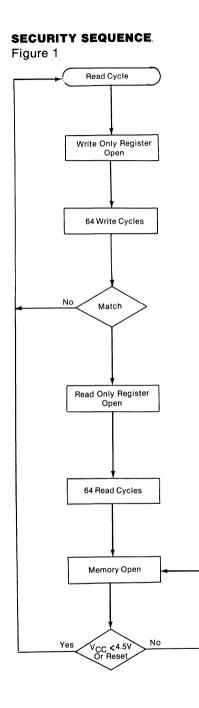

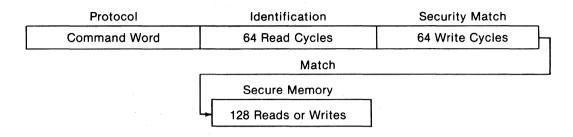

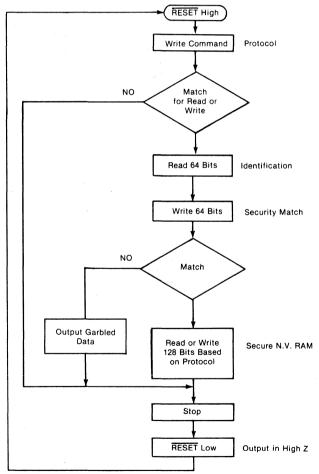

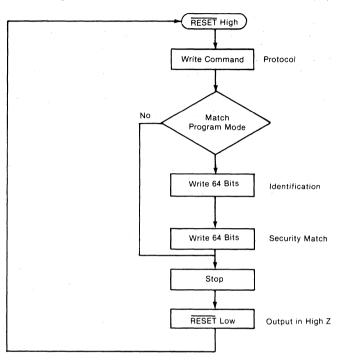

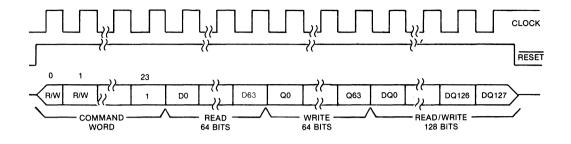

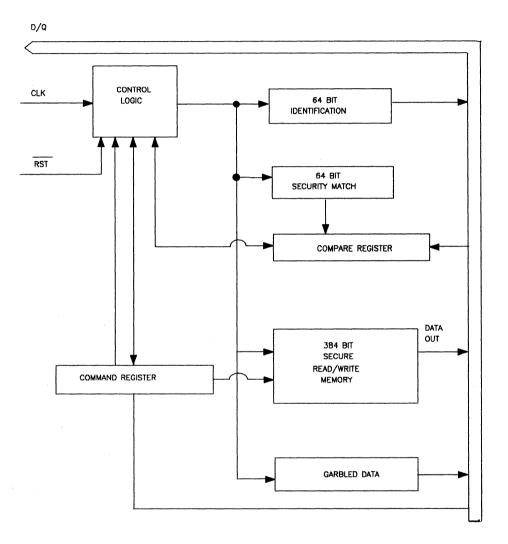

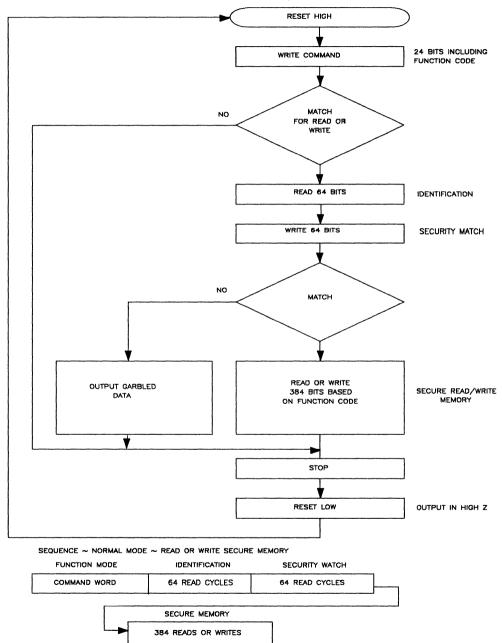

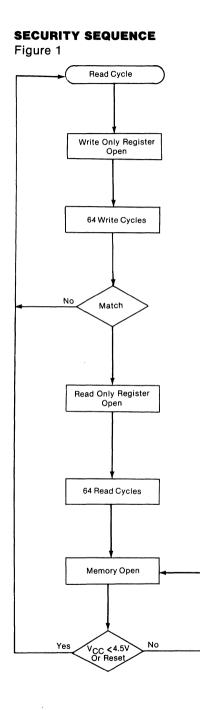

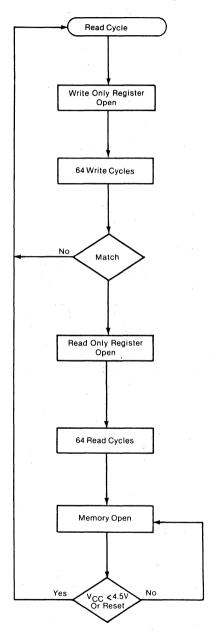

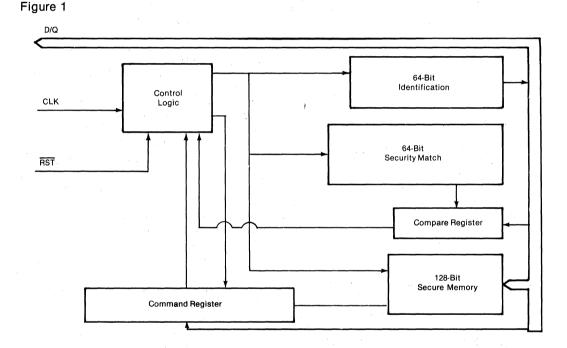

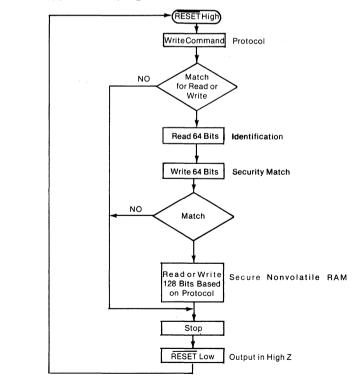

# **Security Products**

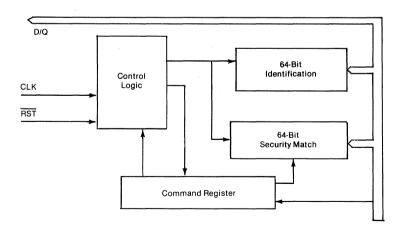

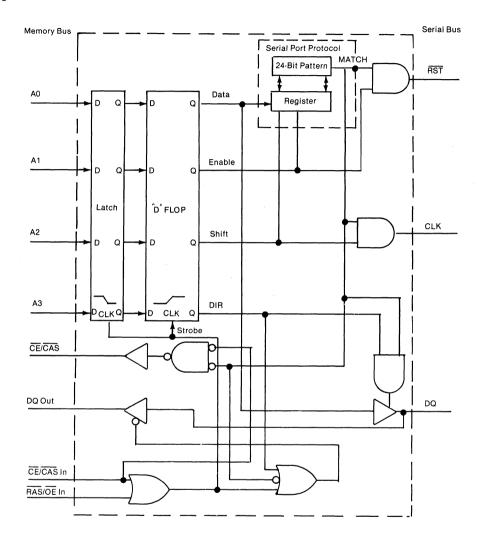

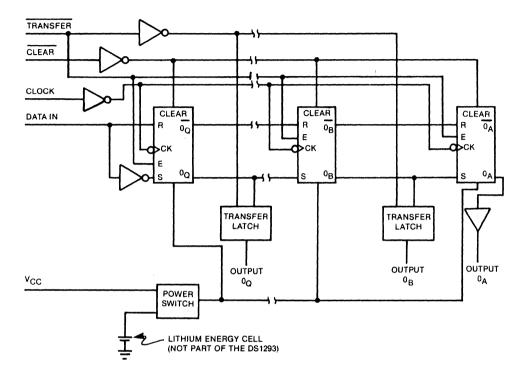

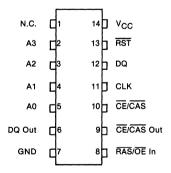

In an information age, there is an increasing demand to provide security for intellectual property and other data beyond legal measures currently available. Prominent examples are publishers and authors of premium-priced personal computer software who have strong motivation to protect their products from unauthorized use. Software based copy protection systems interfere with the need to make legitimate backup copies or execution from hard disks. The Electronic Key is a postage stamp-sized package that is distributed with each software package sold and must be present whenever users want to use the software. This same principle can be applied to controlling access to buildings, automobiles and other equipment.

DS1204 Electronic Key DS1207 Time Key DS1255 Key Ring DS1255C Evaluation Kit for IBM P.C.

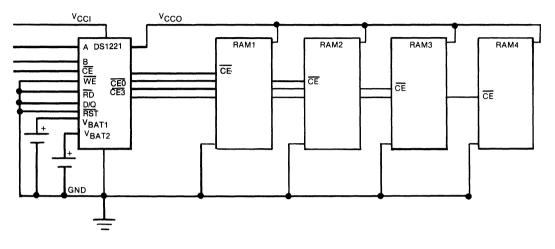

# **Integrated Battery Backup**

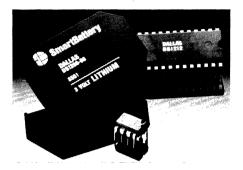

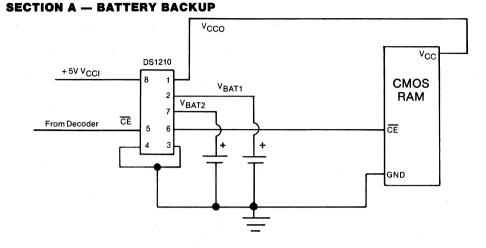

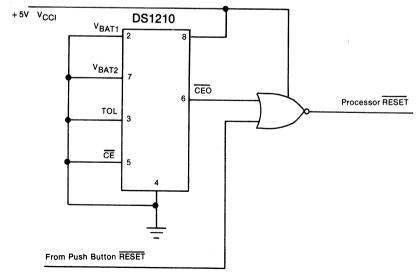

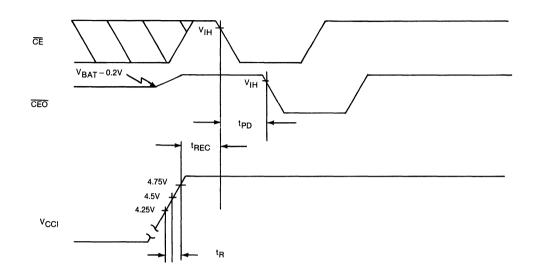

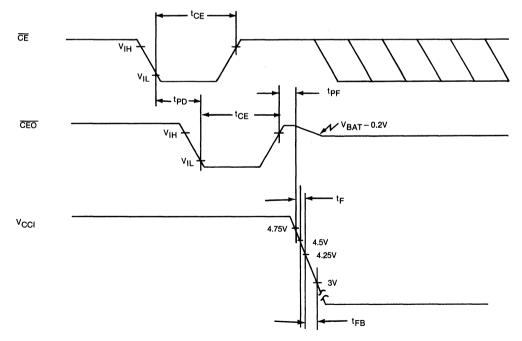

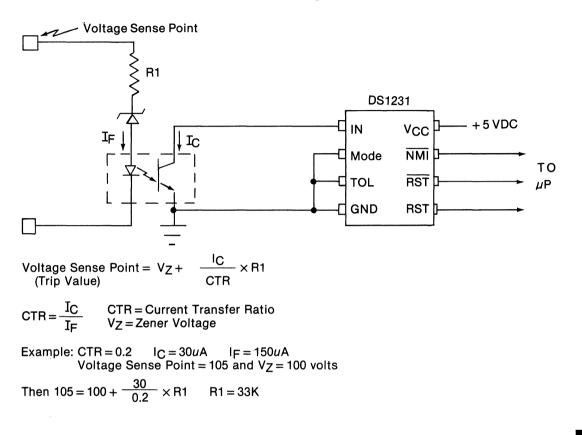

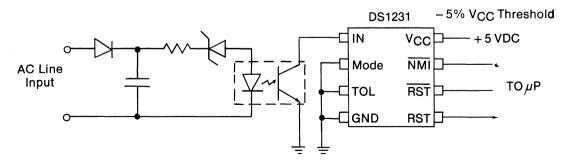

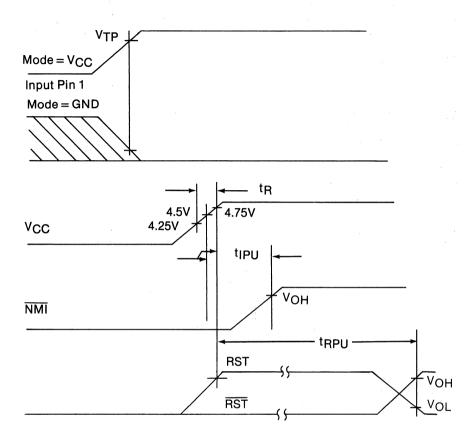

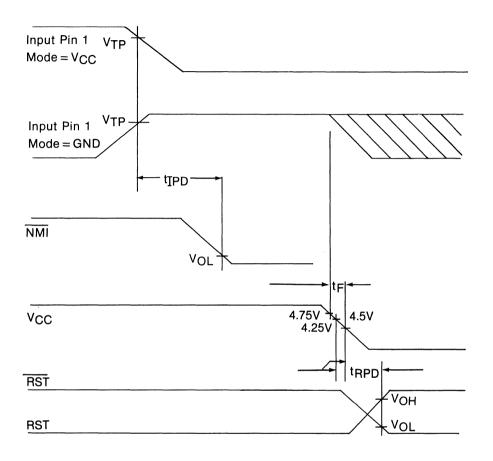

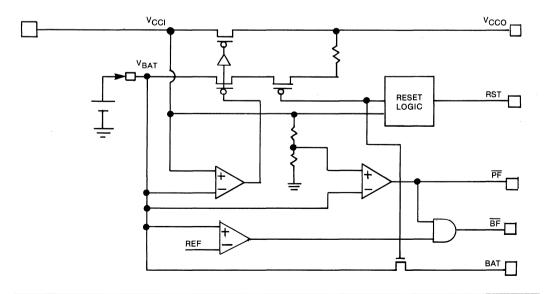

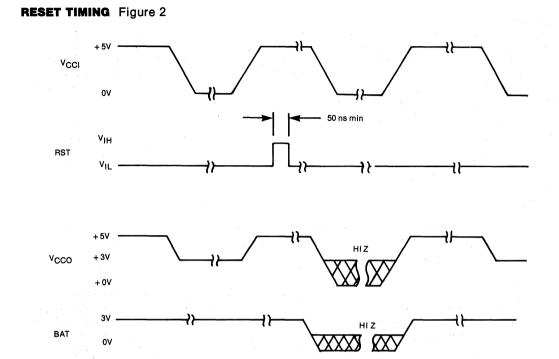

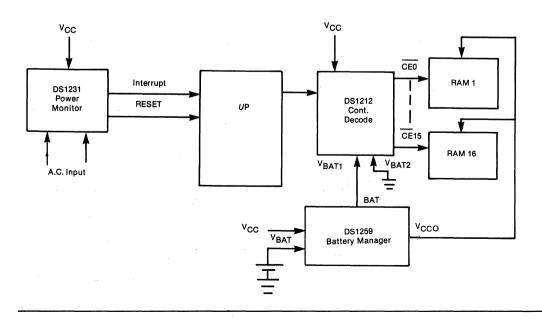

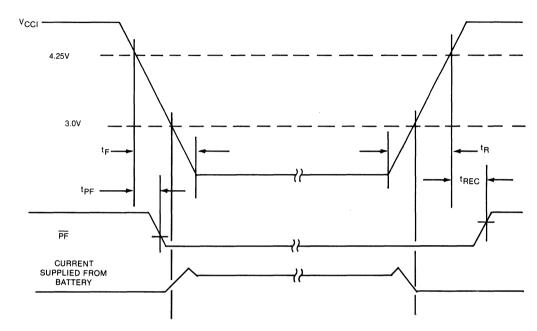

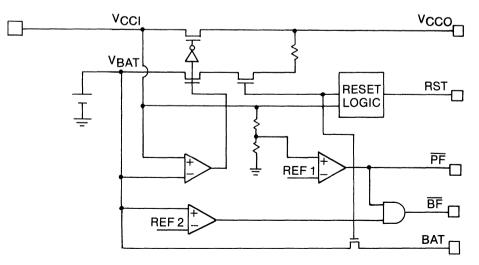

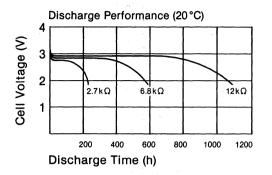

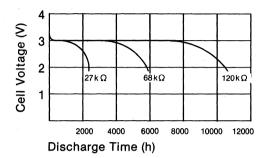

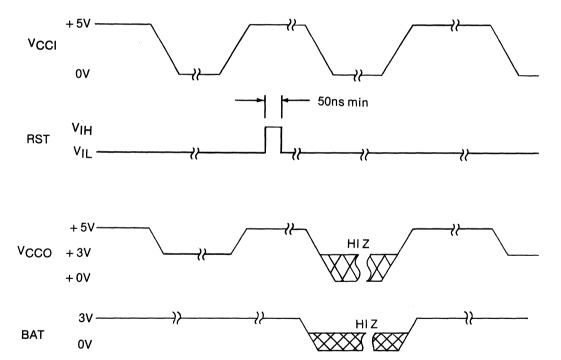

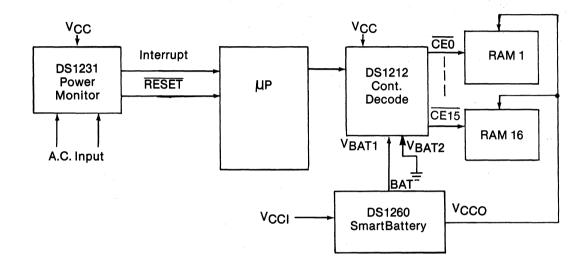

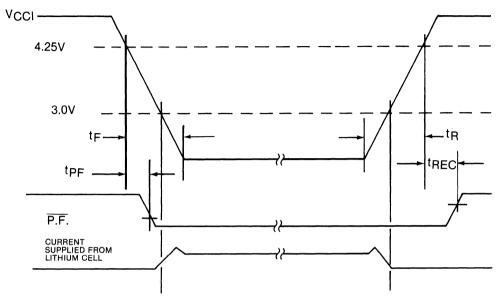

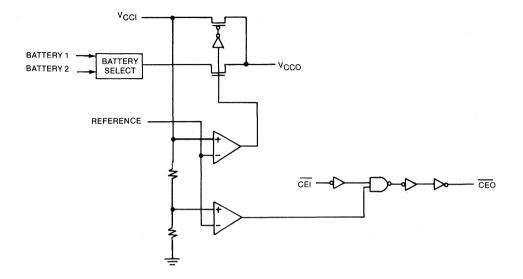

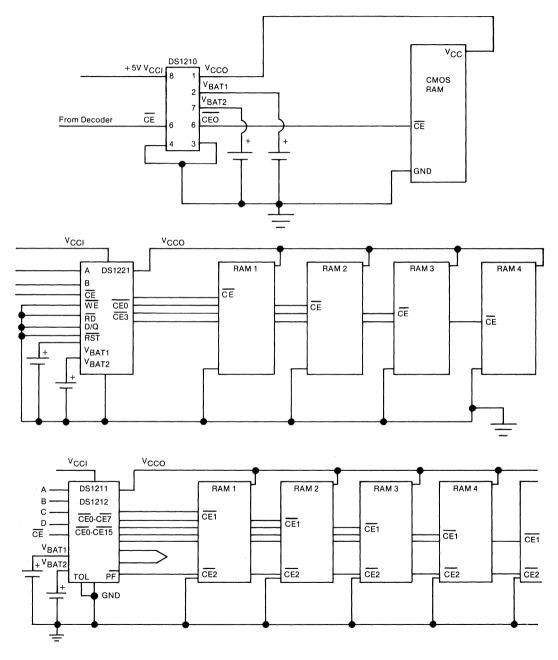

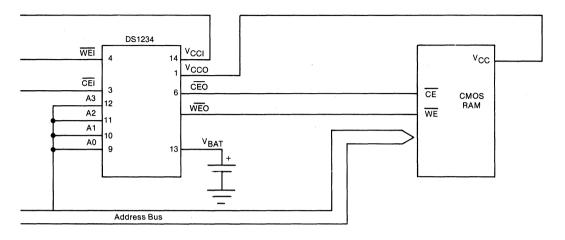

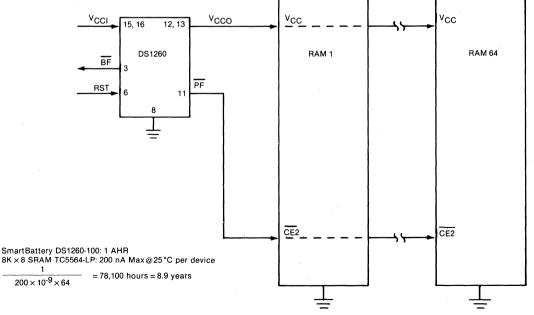

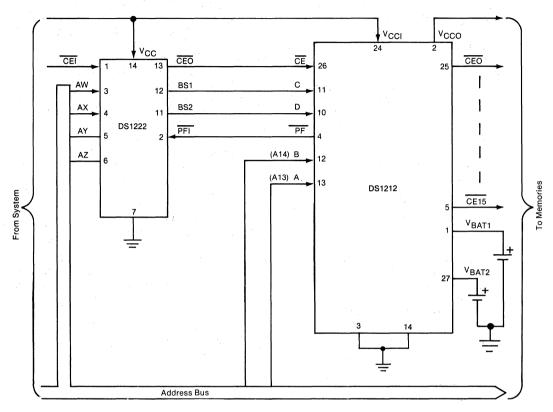

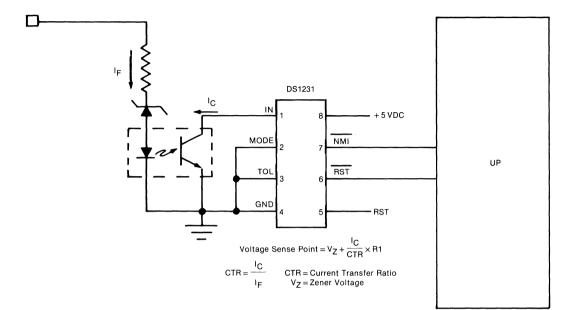

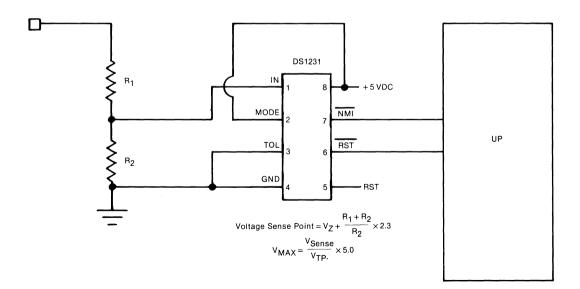

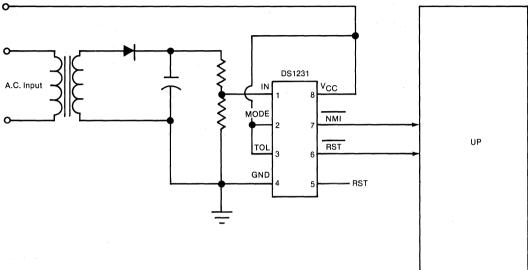

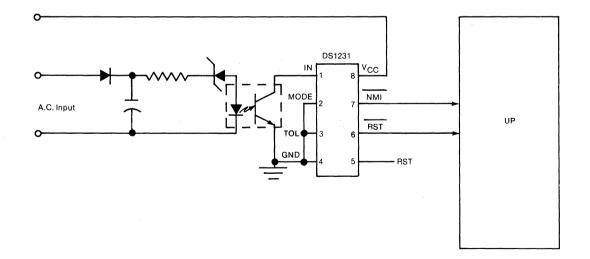

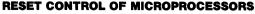

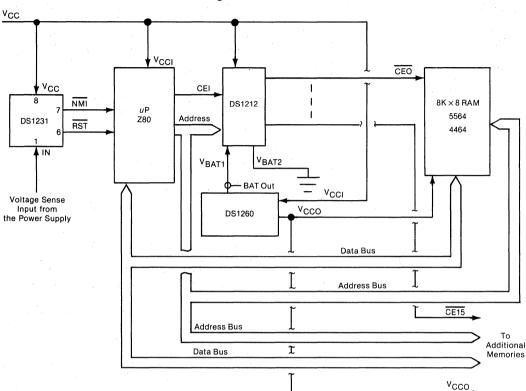

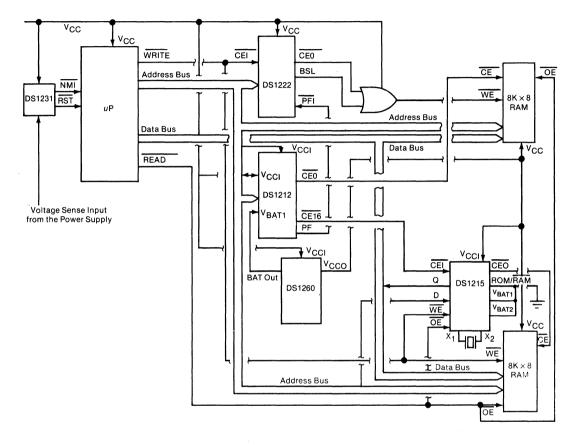

Microprocessor based systems lose information when affected by a loss of power. When system power is resumed, the task that was being performed at the time of power loss must be re-started. Uninteruptible power supplies have historically been provided as relatively expensive, bulky, external units. A solution to this problem is necessitated in industrial automation applications and in systems which are located in remote sites or otherwise difficult to reprogram when information is lost. The Integrated Battery Backup consists of a three part chip set which operates in three steps. First, the Power Monitor warns a microprocessor of an impending power failure before it happens, providing time for critical data to be stored in nonvolatile memory before system power is lost. Second, the Nonvolatile Controller/Decoder converts RAM into nonvolatile memories and safeguards against RAM data loss during power up and down transients, by automatically switching to battery power when system power failure occurs. Third, the SmartBattery supplies uninterruptible power in the absence of system power to maintain data in nonvolatile memory.

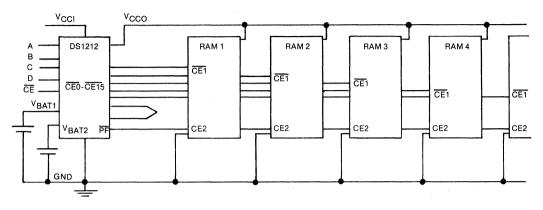

DS1210 Single RAM Controller DS1221 Four RAM Controller DS1211 Eight RAM Controller DS1212 Sixteen RAM Controller DS1234 Conditional RAM controller DS1231 Power Monitor DS1260 Smart Battery DS1259 Battery Manager

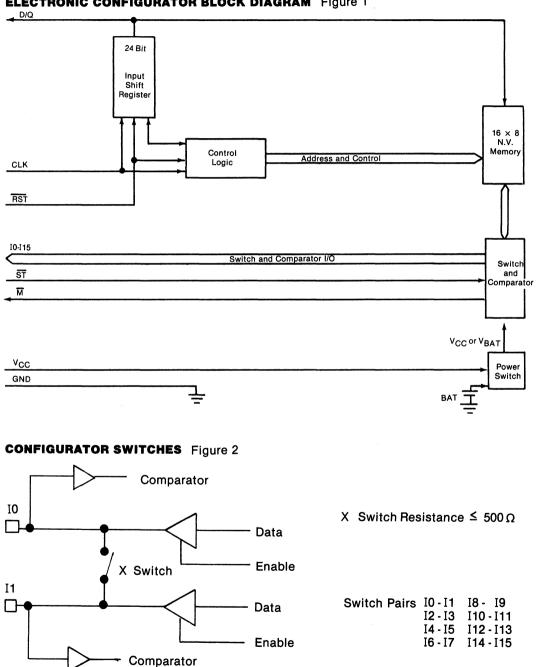

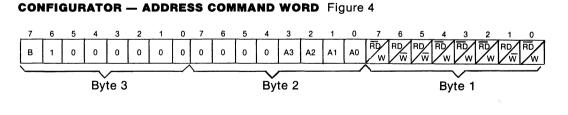

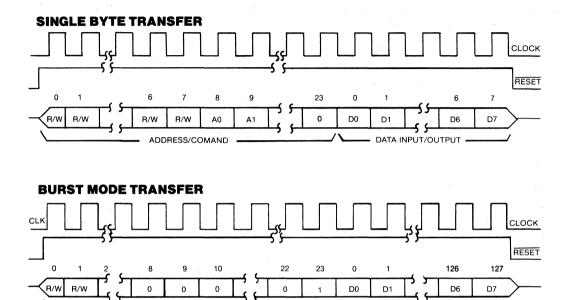

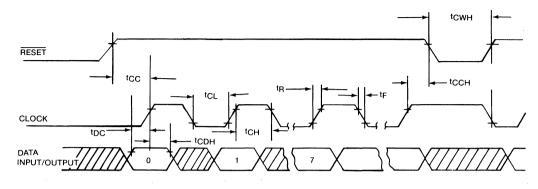

# System Extension

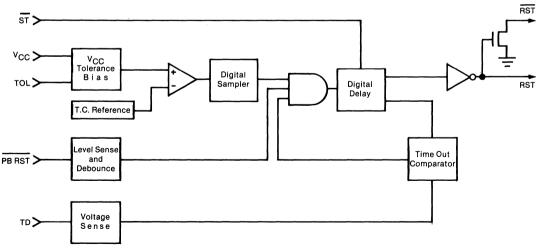

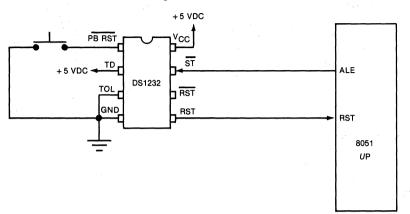

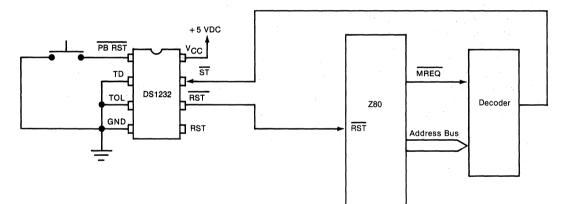

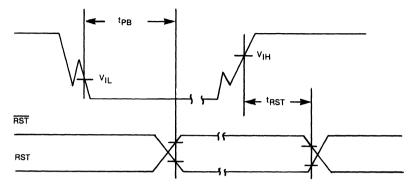

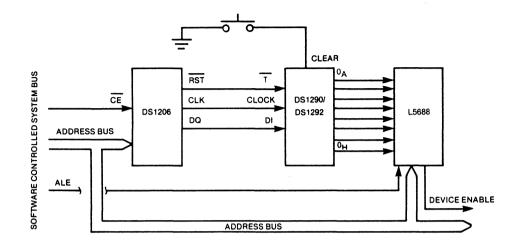

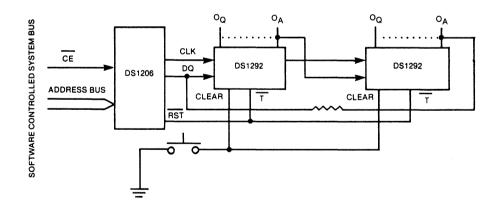

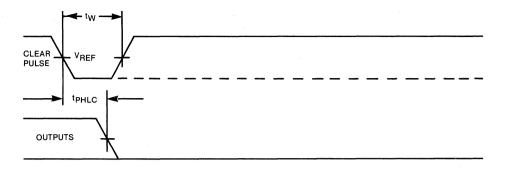

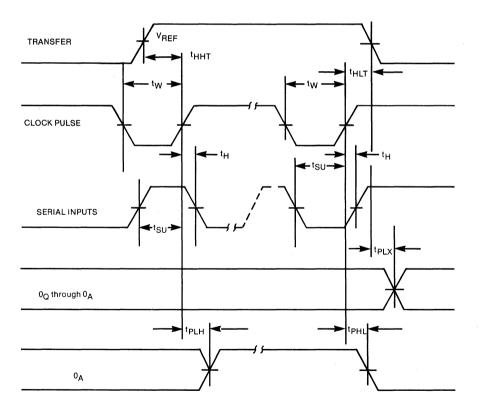

These CMOS products extend the usefulness of systems without encumbering design. The Micro Monitor acts as a "watchdog" for system malfunction by checking the three most important indicators of correct microprocessor operation - power supply, software execution and override push-button. If it detects a problem, the MicroMonitor shuts down the system, then resets it for correct operation. The Eliminator replaces the equivalent of an 8 or 16

station manual DIP switch, thus eliminating burdensome hand setting of mechanical switches. Five volt powered RS232 transceivers are available in both dual and triple versions. The same five volt supply that powers logic generates RS232 voltage levels.

DS1232 MicroMonitor DS1290/91 Eliminator, 8-Station DS1292/93 Eliminator, 16-Station DS1206 Phantom Interface DS1223 Configurator DS1222 Bank Switch DS232/DS1228 RS232 Transceiver, Dual DS1229 RS232 Transceiver, Triple

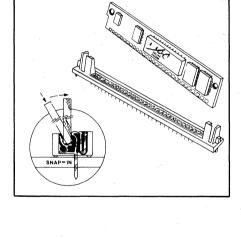

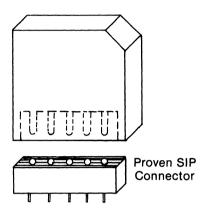

# SipStiks™

Systems snap together with SipStik sub-assemblies from Dallas Semiconductor. SipStiks are leadless carriers of components with high silicon content using JEDEC standard configurations. Their low profile form factor permits high density yet offers the advantages of modularity. These major building blocks are pretested and ready for final assembly into a planar motherboard fitted with AMP MicroEdge connectors as required by a particular application.

DS2217 SRAM SipStik DS2209 DRAM SipStik DS2250 Soft Micro SipStik DS2245 Modem SipStik

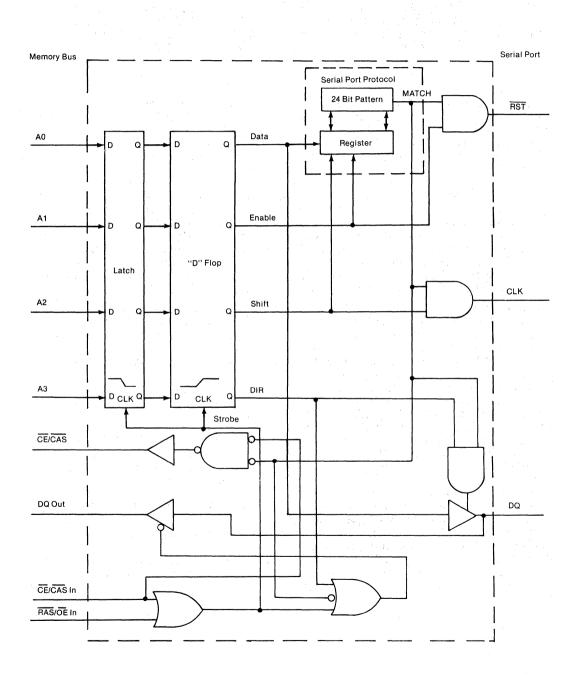

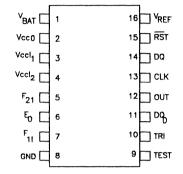

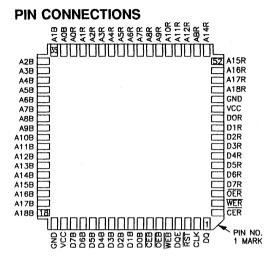

# **Wireless Products**

Portable DS1201 Electronic Tags, DS1204 Keys, or DS5000 Soft Microcontrollers can communicate with a personal computer using CMOS Micropower Receiver/2 to 3 Wire Converter chips and a base RF Communicator. The chips contain wake-up circuitry, amplifiers, filters, timing generators, waveform interpreters, formating and control logic necessary to form a bi-directional 5 foot link between portable units and bases. The ultra low power consumption of the chips enable a single 3 volt lithium energy cell to

be a permanant source of power for receiving, storing, and transmitting data.

DS1203 MicroPower Receiver DS1209 2 to 3 Wire Converter DS1280 Bytewide to 3 Wire Converter DS6068 RF Communicator

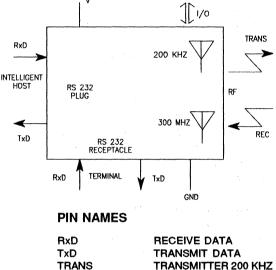

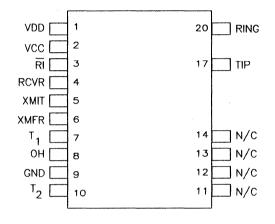

### Modem

These Miniature components comply with FCC part 68 registration. The DS6101 Modem is bell 212A compatible (1200/300 bps) with DTMF generation/ detection, audio mode operation, and advanced line monitoring functions. The DS6103 Modem provides voice synthesis. The DS6112 Data Access Arrangement (DAA) which is included in the Modems above is available as a stand alone interface to the public switch telephone network. DS6151/6153 are Modem evaluation kits that demonstrate the Modem on the IBM/PC/XT/AT.

# **Telecommunications**

An emerging and rapidly growing market exists for high capacity voice, data and video transmission. High capacity digital links in North America and Europe are known as T-1 and CEPT, respectively. Circuits designed for these protocols can substantially shorten the time required for OEMs to develop products that access these networks and can reduce systems sizes. A comprehensive chip set developed by Dallas Semiconductor addresses the requirements of these protocols and includes an integrated circuit that doubles the capacity of existing voice communication links through digital signal processing compression techniques. Complete product specifications available in a supplemental telecommunication data book. DS2180 Transceiver T1

DS2180 Transceiver, T1 DS2181 Transceiver, CEPT DS2175 Transmit/Receive Elastic Store DS2176 Receive Elastic Store DS2186 Transmit Line Interface DS2187 Receive Line Interface DS2190 Network Interface Unit DS2167 ADPCM Processor DS2157 Compression Array

# **Product Data Sheets**

•

1

# **Silicon Timed Circuits**

# Dallas Semiconductor 5 TAP Silicon Delay Line

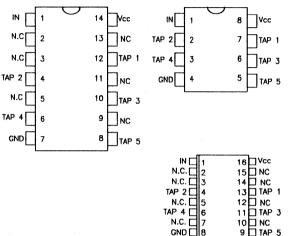

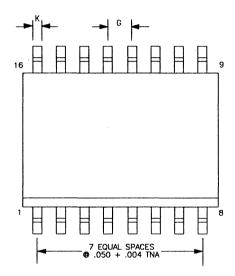

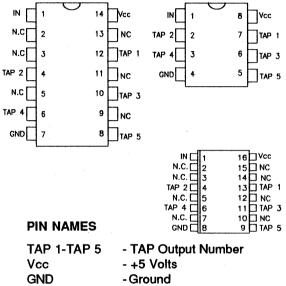

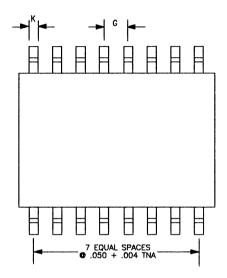

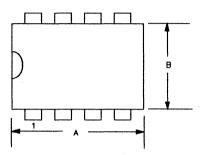

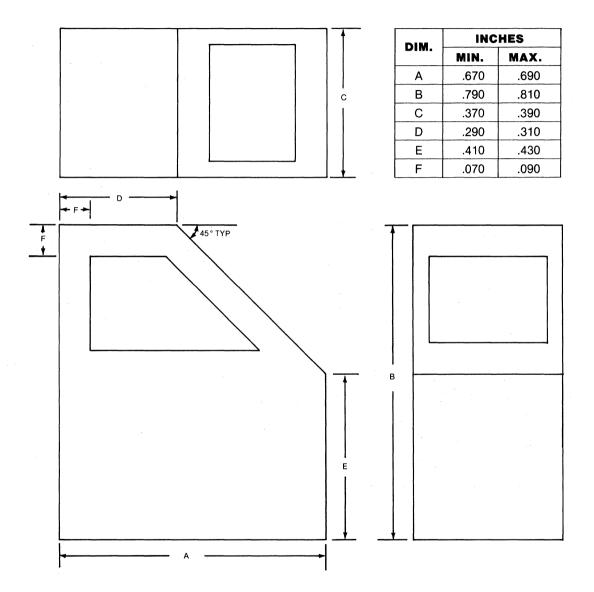

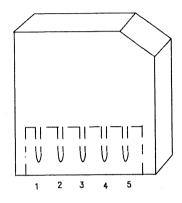

# DS1000 14 Pin DIP DS1000M 8 Pin DIP DS1000S 16 Pin SOIC

# FEATURES

- All silicon time delay

- 5 TAPS equally spaced.

- Delays are stable and precise

- Both leading and trailing edge accuracy

- Standard 14 pin DIP, 8 pin MINI-DIP, or 16 pin SOIC

- Delay tolerance +/- 5%

- Economical

- Auto-insertable

- Low power CMOS

- TTL compatible

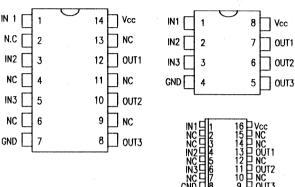

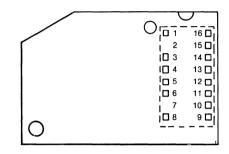

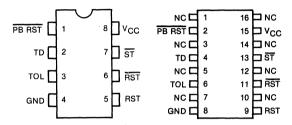

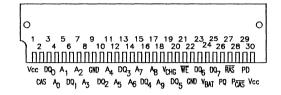

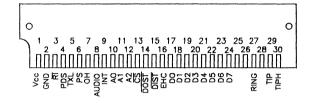

### **PIN CONNECTIONS**

### PIN NAMES

TAP 1-TAP 5 - TAP Output NumberVcc- +5 VoltsGND- GroundNC- No ConnectionIN- Input

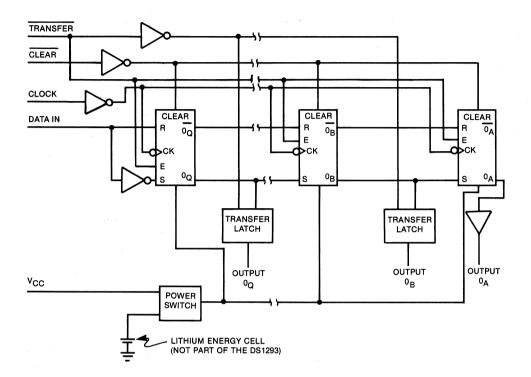

### DESCRIPTION

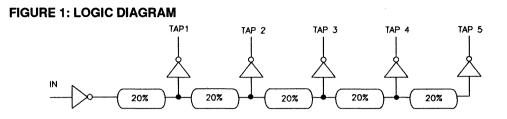

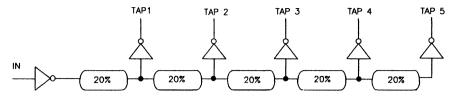

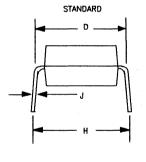

The DS1000 Series Delay Lines have five equally spaced TAPS providing delays from 10 ns to 500 ns. These devices are offered in a standard 14 pin DIP, which is pin compatible with hybrid delay lines. Alternatively 8 pin MINI-DIPS and surface mount packages are available which saves P.C. board area. Since the DS1000 series is an all silicon solution, better economy is achieved when compared to older methods using hybrid techniques.

The DS1000 Series Delay Lines provide a nominal accuracy of +/-5% or +/- 2 ns, which ever is greater. The DS1000 Delay Line reproduces the input logic level at the output after a fixed delay as specified by the dash number extension of the part number. The DS1000 is designed to reproduce both leading and trailing edge with equal precision. Each TAP is capable of driving up to ten 74LS type loads.

# TABLE 1: PART NUMBER DELAY TABLE (tpm, tpu)

| PART NO.   | TAP 1 | TAP2  | ТАРЗ ТАР4 |            | TAP5  |

|------------|-------|-------|-----------|------------|-------|

| DS1000-50  | 10ns  | 20ns  | 30ns      | 40ns       | 50ns  |

| DS1000-60  | 12ns  | 24ns  | 36ns      | 48ns       | 60ns  |

| DS1000-75  | 15ns  | 30ns  | 45ns      | 60ns       | 75ns  |

| DS1000-100 | 20ns  | 40ns  | 60ns      | 80ns       | 100ns |

| DS1000-125 | 25ns  | 50ns  | 75ns      | 100ns      | 125ns |

| DS1000-150 | 30ns  | 60ns  | 90ns      | 90ns 120ns |       |

| DS1000-175 | 35ns  | 70ns  | 105ns     | 140ns      | 175ns |

| DS1000-200 | 40ns  | 80ns  | 120ns     | 160ns      | 200ns |

| DS1000-250 | 50ns  | 100ns | 150ns     | 200ns      | 250ns |

| DS1000-500 | 100ns | 200ns | 300ns     | 400ns      | 500ns |

#### **ABSOLUTE MAXIMUM RATINGS\***

Voltage on a pin to ground:-1.0Vto + 7.0V Operating temperature: 0°C to 70°C Storage temperature: -55°C to + 125°C Soldering temperature: 260°C for 10 seconds Short circuit output current: 50mA for 1 second \*This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

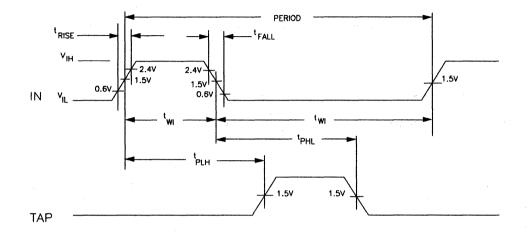

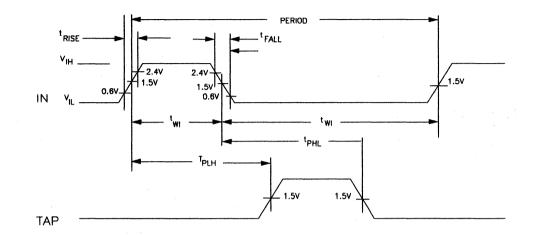

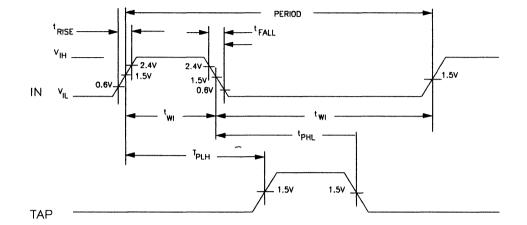

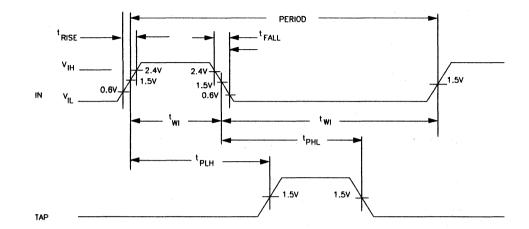

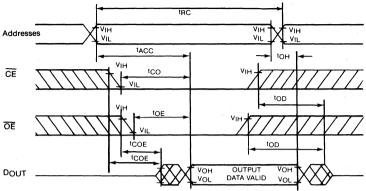

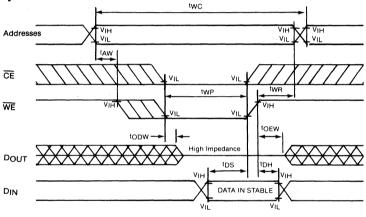

#### Terminology

<u>Period</u> The time elapsed between the leading edge of the first pulse and the leading edge of the following pulse.

$t_{WI}$  (Pulse Width) The elapsed time on the pulse between the 1.5V point on the leading edge and the 1.5V point on the trailing edge or the 1.5V point on the trailing edge and the 1.5V point on the leading edge.

$t_{RISE}$  (Input Rise Time) The elapsed time between the 20% and the 80% point on the leading edge of the input pulse.

$t_{FALL}$  (Input Fall Time) The elapsed time between the 80% and the 20% point on the railing edge of the input pulse.

$t_{PLH}$  (Time Delay, Rising) The elapsed time between the 1.5V point on the leading edge of the input pulse and the 1.5V point on the leading edge of any TAP output pulse.  $t_{PHL}$  (Time Delay, Falling) The elapsed time between the 1.5V point on the trailing edge of the input pulse and the 1.5V point on the trailing edge of any TAP output pulse.

#### Notes

- 1.)All voltages are referenced to ground.

- 2.)Measured with outputs open, minimum period.

- 3.)Vcc=5V @25°C Delays accurate on both rising and falling edges within +/- 2 ns, or 5%.

- 4.) See Test Conditions (following page).

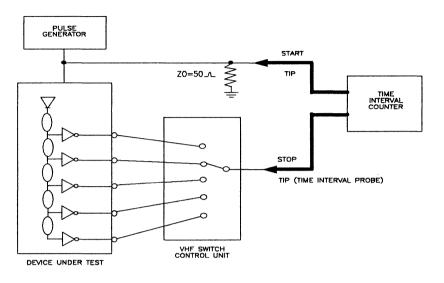

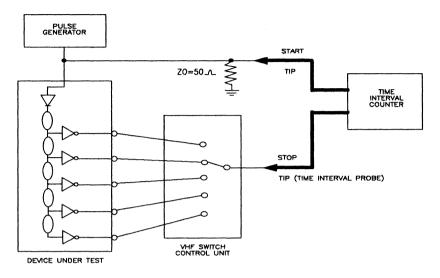

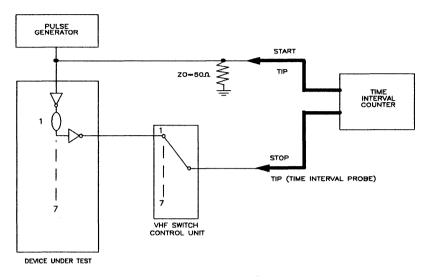

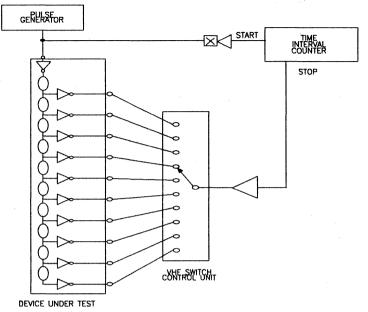

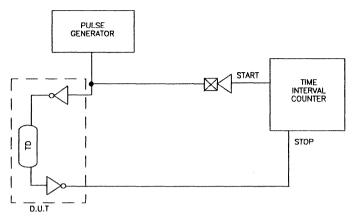

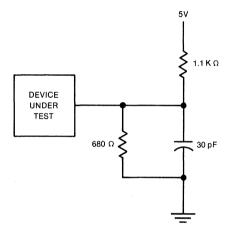

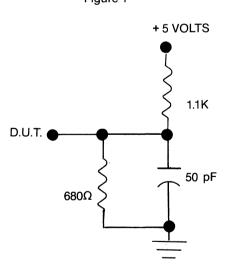

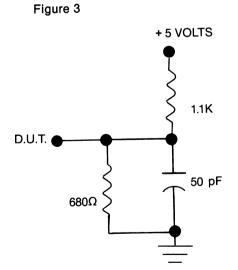

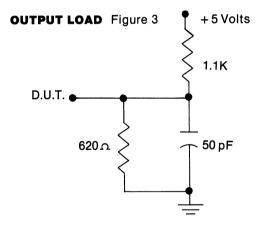

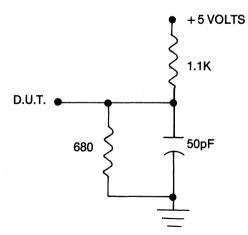

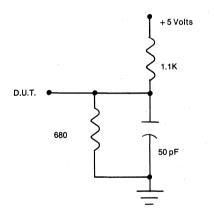

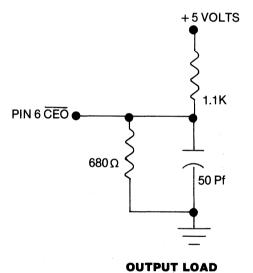

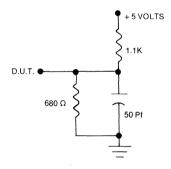

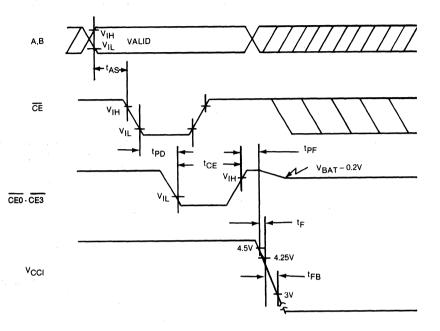

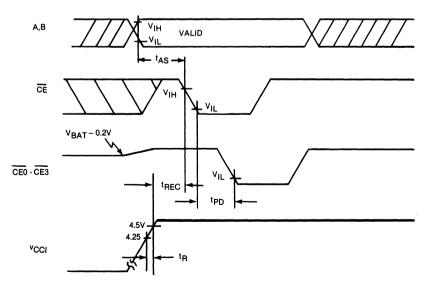

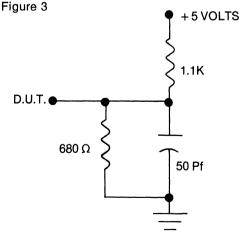

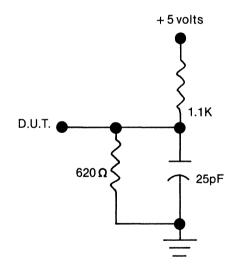

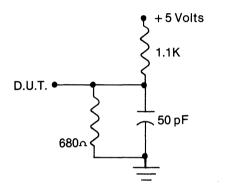

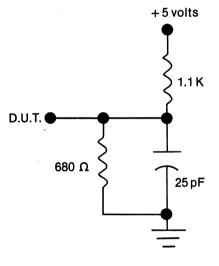

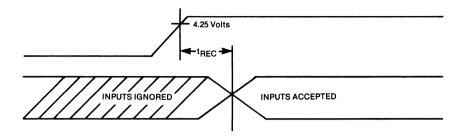

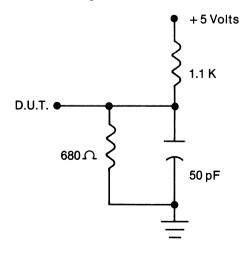

# FIGURE 3: DALLAS SEMICONDUCTOR TEST CIRCUIT

### **Test Setup Description**

Figure 3 illustrates the hardware configuration used for measuring the timing parameters on the DS1000. The input waveform is produced by a precision pulse generator under software control. Time delays are measured by a time interval counter (20 ps resolution) connected between the input and each TAP. Each TAP is selected and connected to the counter by a VHF switch control unit.

The measurement setup is calibrated by TDR (time domain reflectometry) techniques. All measurements are fully automated, with each instrument controlled by a central computer over an IEEE 488 bus.

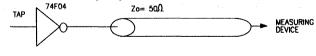

### **Test Conditions**

Input: Ambient Temperature: 25°C+/-3°C Supply Voltage (Vcc): 5.0V+/-0.1V Input Pulse: High = 3.0V+/-0.1V Low = 0.0V+/-0.1V Source Impedancc: 50 ∩Max. Rise and FAII Time: 3.0 ns Max. (measured between 0.6V and 2.4V) Pulse Width = 500 ns Period= 1us

#### Note:

Above conditions are for test only and do not restrict the operation of the device under other conditions.

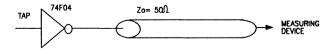

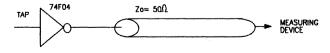

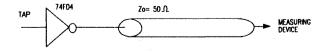

#### Output:

Each output is loaded with a 74F04. Delay is measured at the 1.5V level on the rising and falling edge.

# D.C. ELECTRICAL CHARACTERISTICS

# (0°C to 70°C, Vcc = 5.0V +/- 5%)

| PARAMETER                    | SYMBOL<br>COND. | TEST                                | MIN  | ТҮР  | MAX  | UNITS | NOTES |

|------------------------------|-----------------|-------------------------------------|------|------|------|-------|-------|

| Supply Voltage               | Vcc             |                                     | 4.75 | 5.00 | 5.25 | v     | 1     |

| High Level<br>Input Voltage  | V <sub>IH</sub> |                                     | 2.2  |      | 5.5  | ۷     | 1     |

| Low Level<br>Input Voltage   | V <sub>IL</sub> |                                     | -0.5 |      | 0.8  | V     | 1     |

| Input Leakage<br>Current     | I,              | 0.0V∕≦VI <i>≦</i> Vcc               | -1.0 |      | 1.0  | иА    |       |

| Active Current               | ۱ <sub>œ</sub>  | Vcc= Max;<br>Period= Min.           |      |      | 35.0 | mA    |       |

| High Level<br>Output Current | I <sub>OH</sub> | Vcc= Min.<br>V <sub>он</sub> =2.4V  | 1.0  |      | ·    | mA    |       |

| Low Level<br>Output Current  | la              | Vcc= Min.<br>V <sub>oL</sub> = 0.5V | 12.0 |      |      | mA    |       |

# A.C. ELECTRICAL CHARACTERISTICS

(T<sub>A</sub>= 25°C, Vcc=5V+/- 5%)

| PARAMETER                             | SYMBOL           | MIN                  | ТҮР     | MAX    | UNITS | NOTES |

|---------------------------------------|------------------|----------------------|---------|--------|-------|-------|

| Input Pulse Width                     | t <sub>wi</sub>  | 40% of<br>TAP 5      |         |        | ns    |       |

| Input to TAP delay<br>(leading edge)  | t <sub>PLH</sub> | note 3               | Table 1 | note 3 | ns    | 4     |

| Input to TAP Delay<br>(trailing edge) | t <sub>PHL</sub> | note 3               | Table 1 | note 3 | ns    | 4     |

|                                       | Period           | 4 (t <sub>wi</sub> ) |         |        | ns    |       |

# CAPACITANCE

(T<sub>A</sub>= 25°C)

| PARAMETER          | SYMBOL         | MIN | ТҮР | МАХ | UNITS | NOTES |

|--------------------|----------------|-----|-----|-----|-------|-------|

| Input Capacitance  | C <sub>N</sub> |     | 5   | 10  | рF    |       |

| Output Capacitance | Car            |     | 5   | 10  | pF    |       |

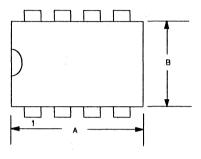

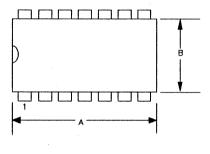

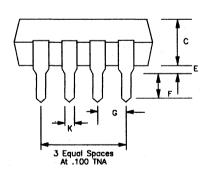

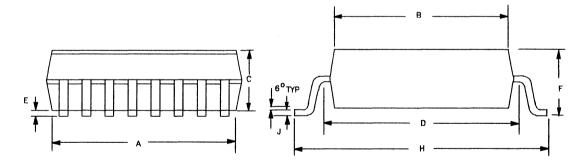

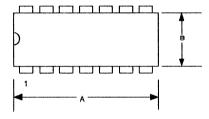

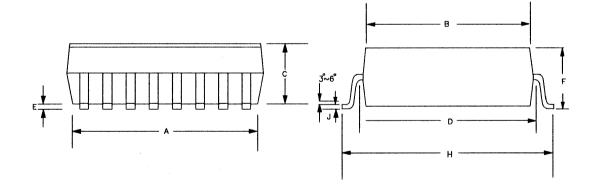

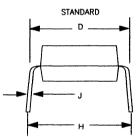

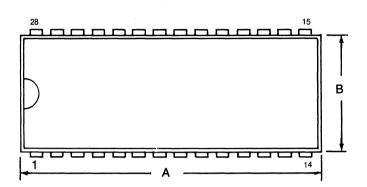

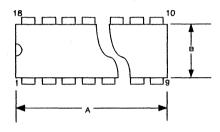

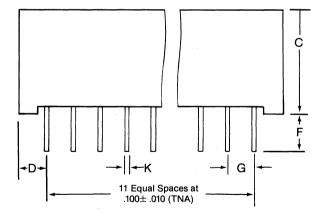

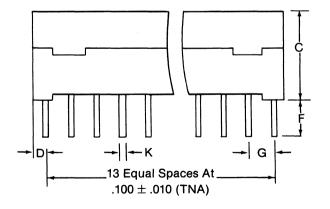

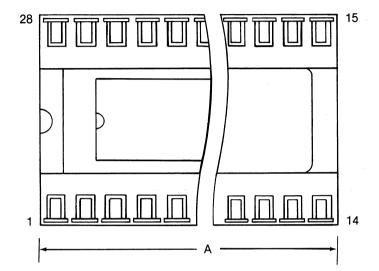

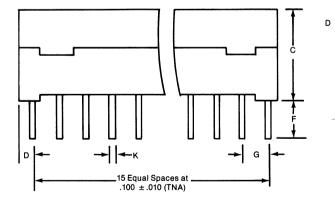

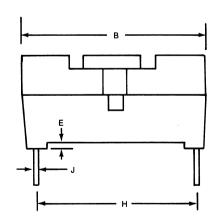

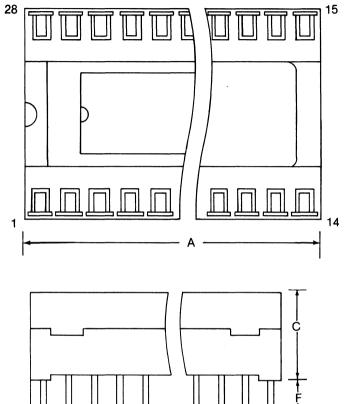

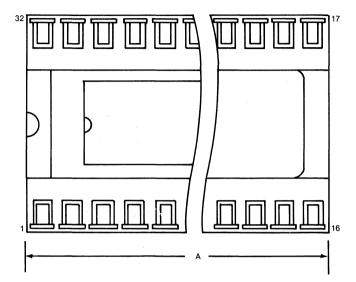

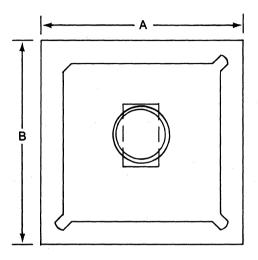

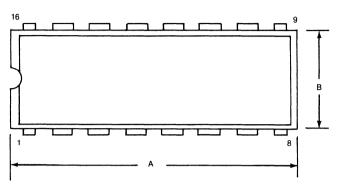

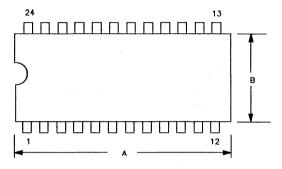

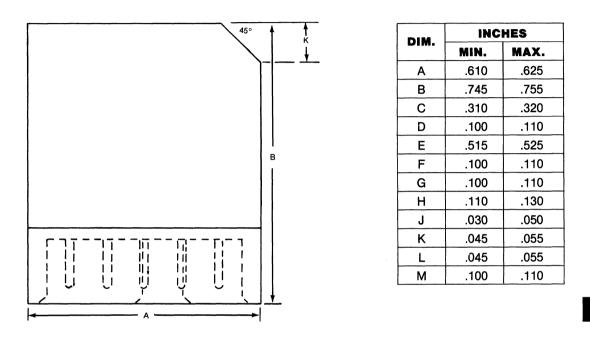

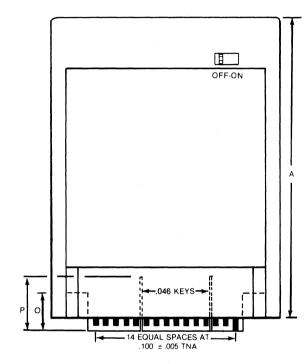

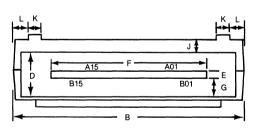

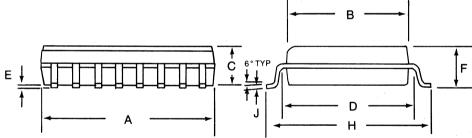

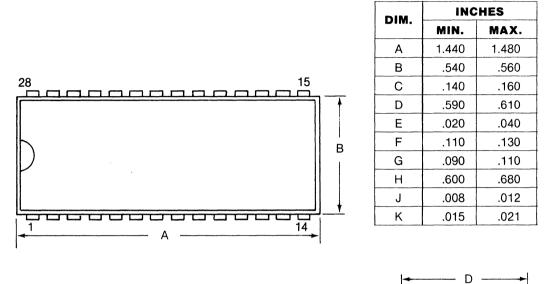

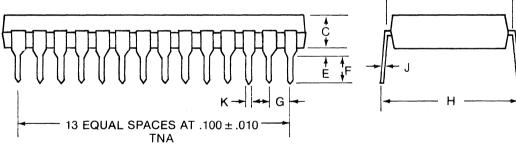

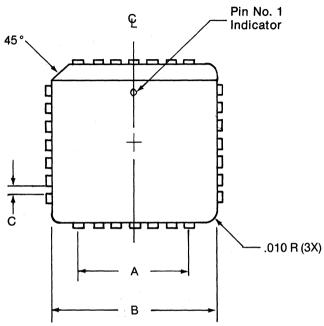

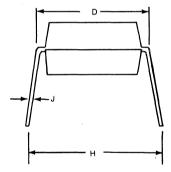

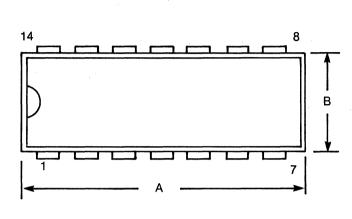

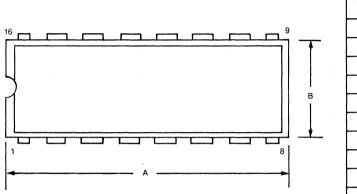

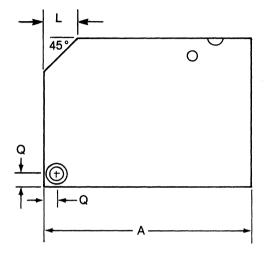

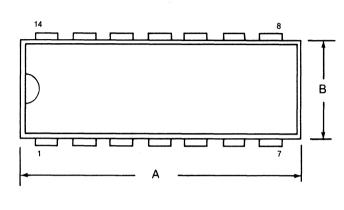

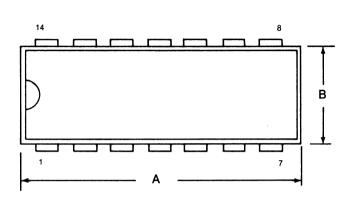

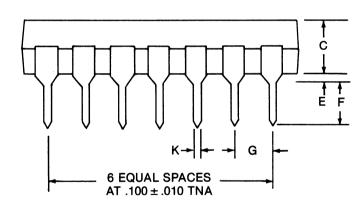

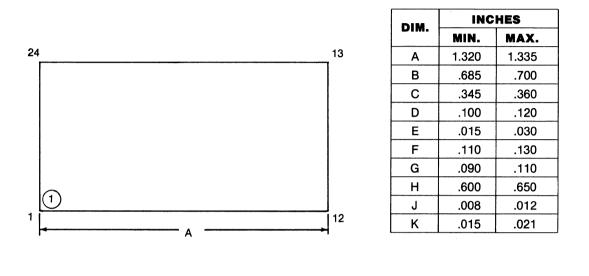

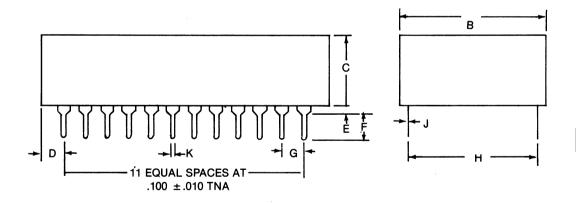

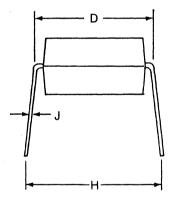

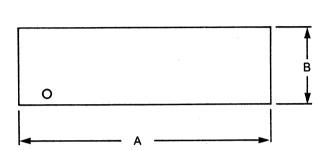

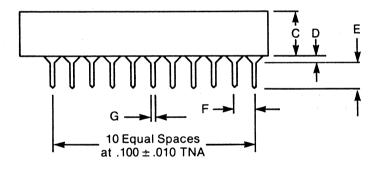

# SILICON DELAY LINE DS1000 14 Pin DIP

-

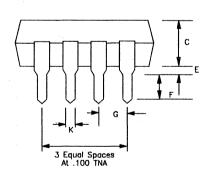

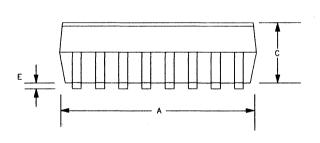

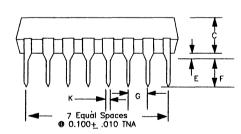

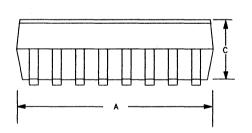

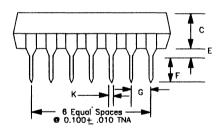

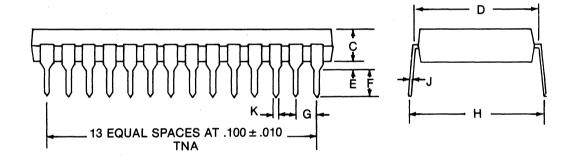

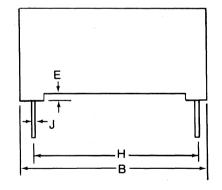

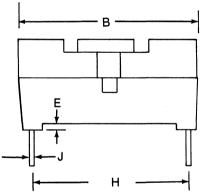

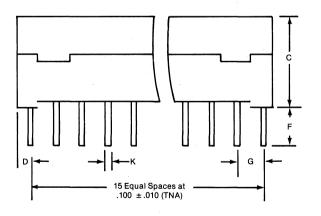

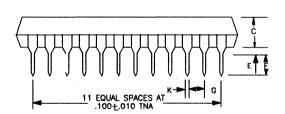

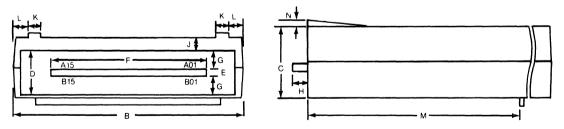

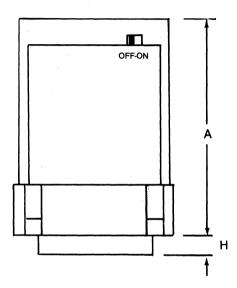

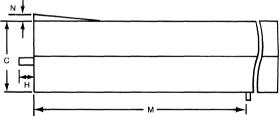

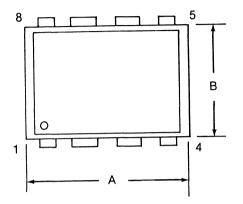

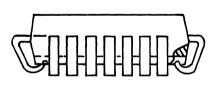

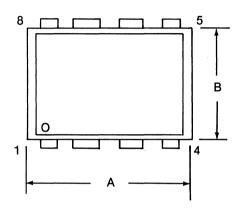

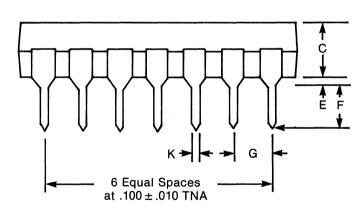

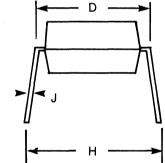

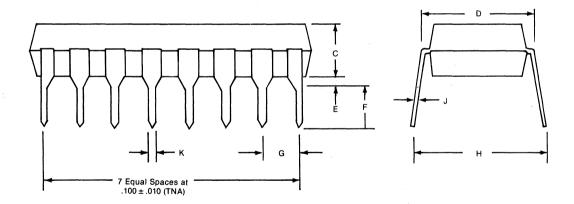

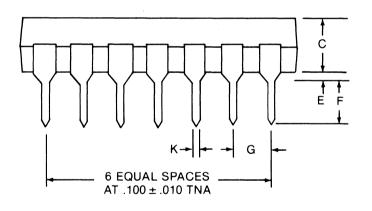

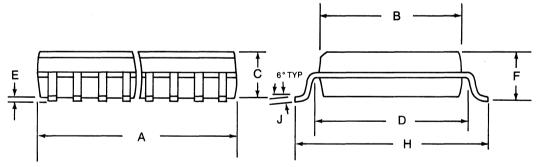

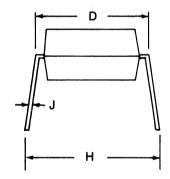

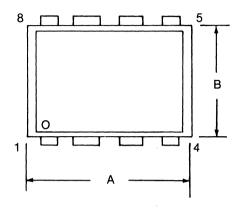

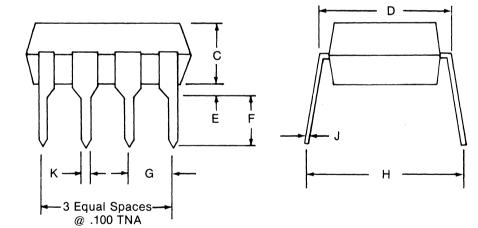

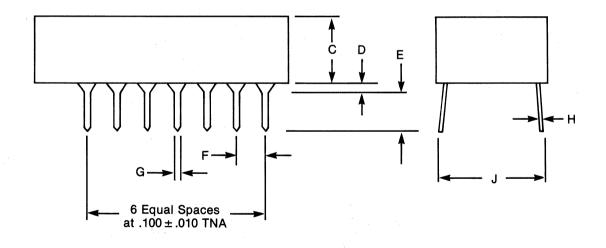

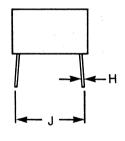

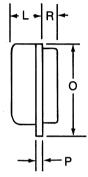

# SILICON DELAY LINE DS1000M 8 Pin DIP

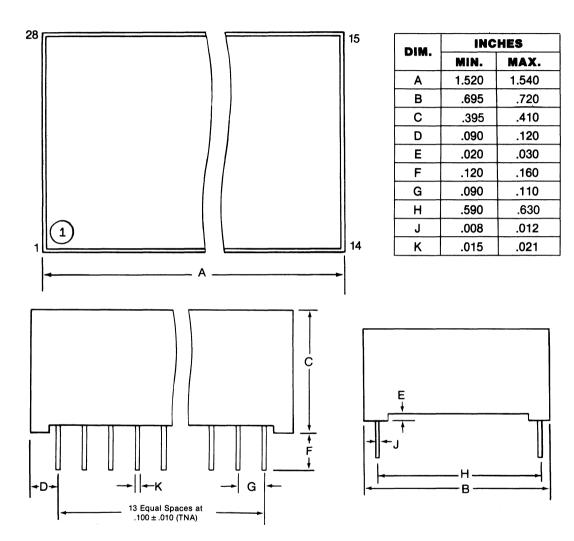

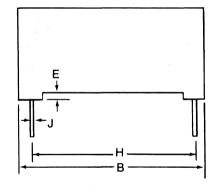

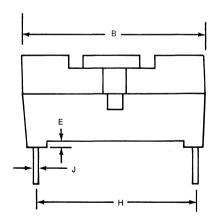

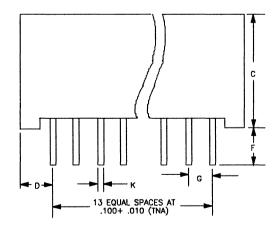

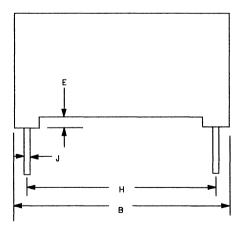

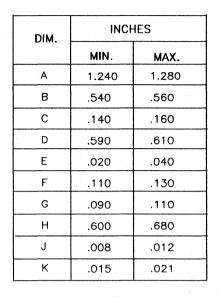

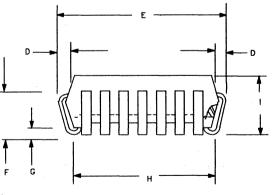

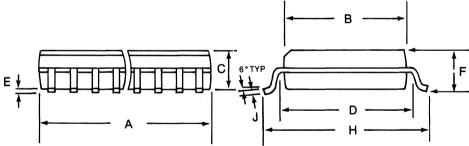

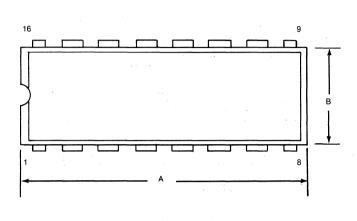

| DIM. | INCHES |       |  |

|------|--------|-------|--|

|      | MIN.   | MAX.  |  |

| Α    | 0.360  | 0.400 |  |

| В    | 0.240  | 0.260 |  |

| С    | 0.120  | 0.140 |  |

| D.   | 0.290  | 0.310 |  |

| E    | 0.020  | 0.040 |  |

| F    | 0.110  | 0.130 |  |

| G    | 0.090  | 0.110 |  |

| н    | 0.300  | 0.350 |  |

| J    | 0.008  | 0.012 |  |

| К    | 0.015  | 0.021 |  |

| L    | 0.040  | 0.060 |  |

| М    | 0.370  | 0.420 |  |

| N    | 0.160  | 0.180 |  |

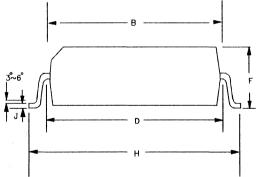

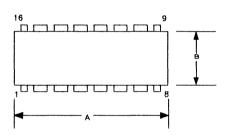

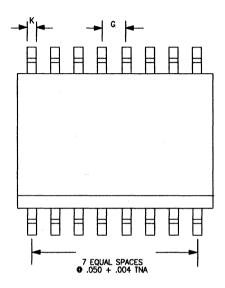

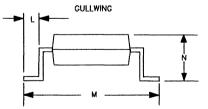

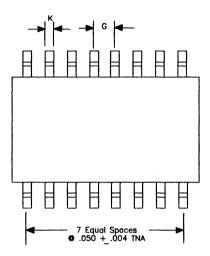

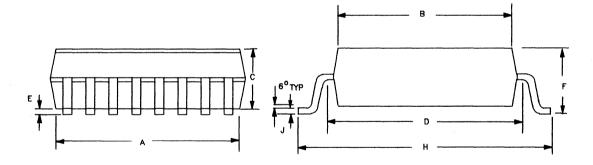

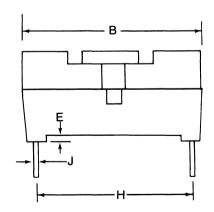

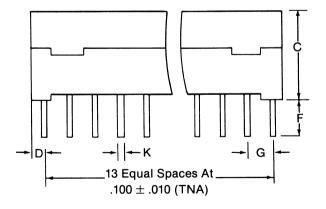

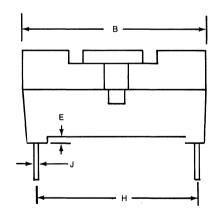

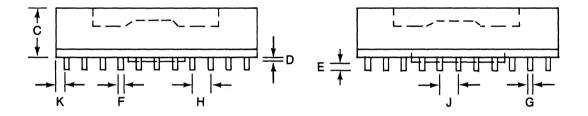

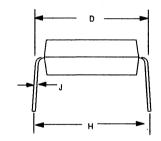

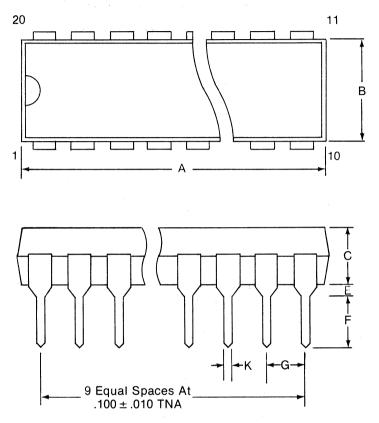

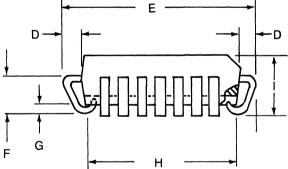

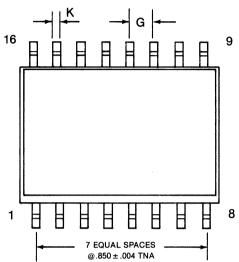

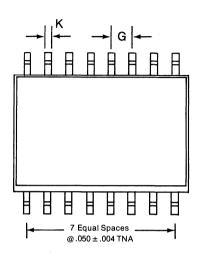

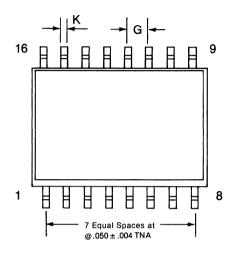

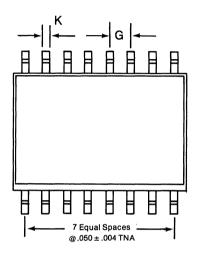

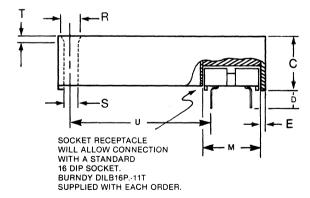

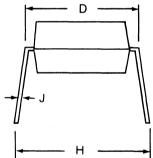

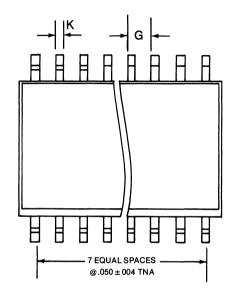

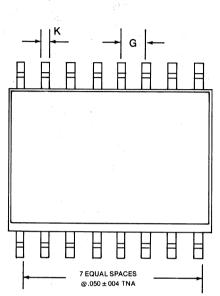

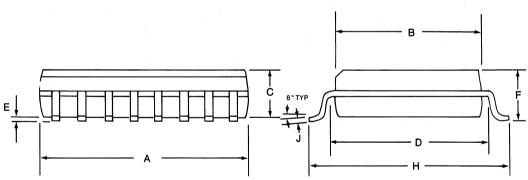

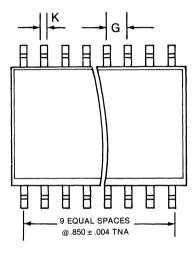

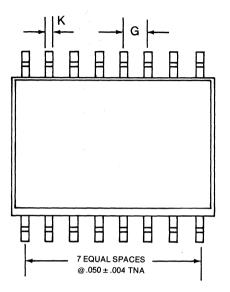

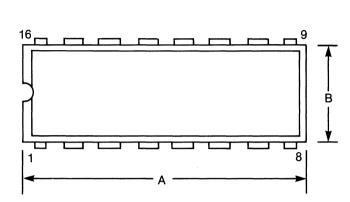

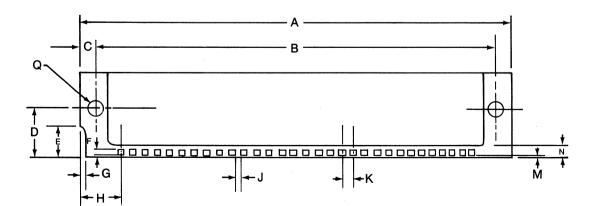

# SILICON DELAY LINE DS1000S 16 Pin SOIC

\*\*\*\*

| DIM. | INCHES |      |  |

|------|--------|------|--|

| 2    | MIN.   | MAX. |  |

| А    | .403   | .411 |  |

| В    | .290   | .296 |  |

| С    | .089   | .095 |  |

| D    | .325   | .330 |  |

| E    | .008   | .012 |  |

| F    | .097   | .105 |  |

| G    | .046   | .054 |  |

| н    | .402   | .410 |  |

| J    | .006   | .011 |  |

| к    | .013   | .019 |  |

# **Dallas Semiconductor** 5 Tap Silicon Delay Line

# DS1005 14 Pin DIP DS1005M 8 Pin DIP DS1005S 16 Pin SOIC

### FEATURES

- All silicon time delay

- 5 TAPS equally spaced. Delay tolerance +/- 2 ns

- Stable and precise over temperature and voltage range

- Leading and trailing edge accuracy

- Standard 14 pin DIP, 8 pin MINI-DIP, or 16 pin SOIC

- Auto-insertable

- Low power CMOS

- TTL compatible

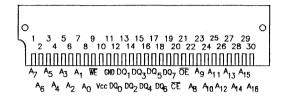

#### **PIN CONNECTIONS**

- No Connection

- Input

NC

IN

#### DESCRIPTION

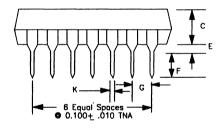

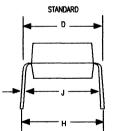

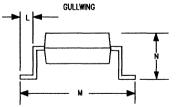

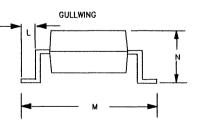

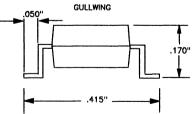

The DS1005 Delay Line Product Family provides five equally spaced TAPS with delays ranging from 10 ns to 500 ns, with an accuracy of +/- 2 ns. These devices are offered in a standard 14 pin DIP, compatible with existing delay line products. A space saving 8 pin MINI-DIP is also available. The 14 pin DIP, the 8 pin MINI-DIP, and SOIC packaging are available in a surface mountable "gullwing" construction. Since the DS1005 is an all silicon solution, better economy and reliability are achieved when compared to older methods using hybrid technology. The DS1005 Delay Line reproduces the input logic level at each TAP after the fixed delay specified by the "dash number" in Table 1. The device is designed to produce both the leading and trailing edge delays with equal precision. Each TAP is capable of driving up to ten 74LS loads.

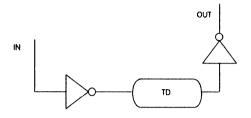

### FIGURE 1: LOGIC DIAGRAM

## TABLE 1 PART NUMBER DELAY TABLE (t<sub>PHL</sub>, t<sub>PLH</sub>)

| PART NO.   | TAP 1 | TAP2  | ТАРЗ  | TAP4  | TAP5  |

|------------|-------|-------|-------|-------|-------|

| DS1005-50* | 10ns  | 20ns  | 30ns  | 40ns  | 50ns  |

| DS1005-60* | 12ns  | 24ns  | 36ns  | 48ns  | 60ns  |

| DS1005-75* | 15ns  | 30ns  | 45ns  | 60ns  | 75ns  |

| DS1005-100 | 20ns  | 40ns  | 60ns  | 80ns  | 100ns |

| DS1005-125 | 25ns  | 50ns  | 75ns  | 100ns | 125ns |

| DS1005-150 | 30ns  | 60ns  | 90ns  | 120ns | 150ns |

| DS1005-175 | 35ns  | 70ns  | 105ns | 140ns | 175ns |

| DS1005-200 | 40ns  | 80ns  | 120ns | 160ns | 200ns |

| DS1005-250 | 50ns  | 100ns | 150ns | 200ns | 250ns |

| DS1005-500 | 100ns | 200ns | 300ns | 400ns | 500ns |

\*Consult Dallas Semiconductor for availability

### **ABSOLUTE MAXIMUM RATINGS\***

Voltage on a pin to ground: -1.0Vto + 7.0V Operating temperature: 0°C to 70°C Storage temperature: -55°C to + 125°C Soldering temperature: 260°C for 10 seconds Short circuit output current: 50mA for 1 second

This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

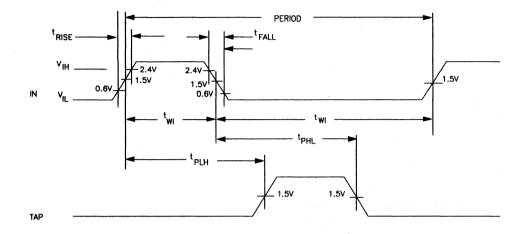

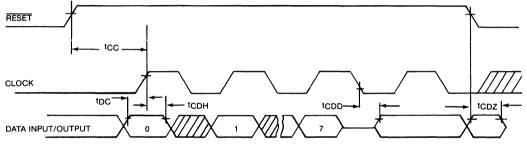

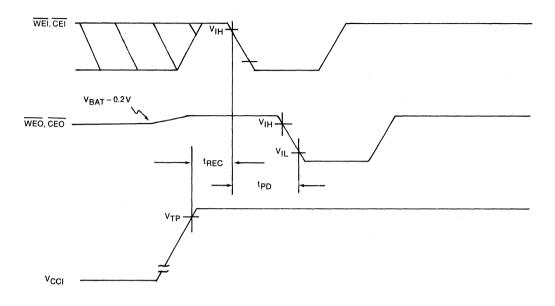

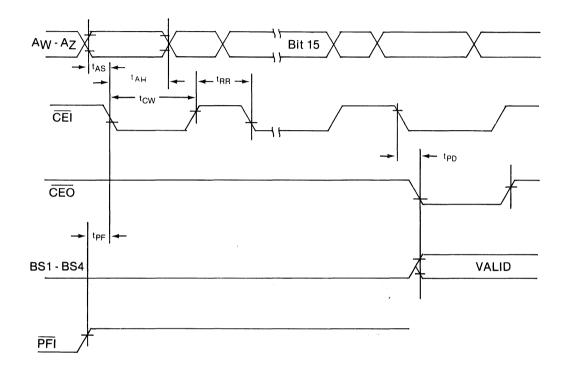

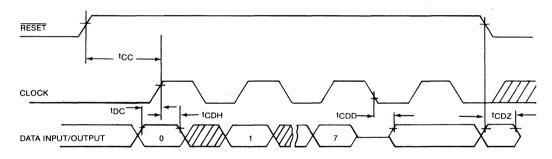

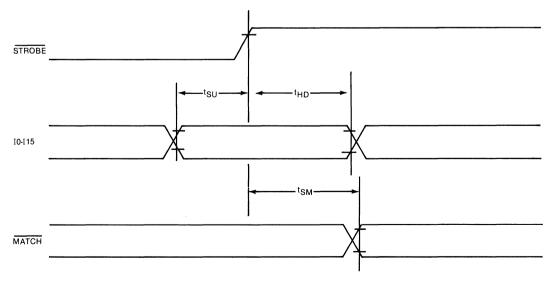

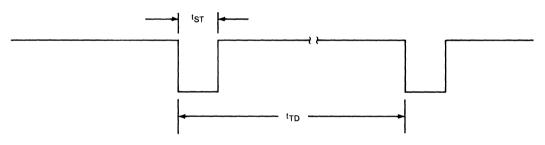

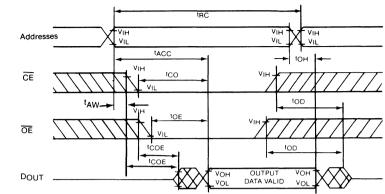

### FIGURE 2: TIMING DIAGRAM- SILICON DELAY LINE

#### Terminology

<u>Period</u> The time elapsed between the leading edge of the first pulse and the leading edge of the following pulse.

$t_{wl}$  (Pulse Width) The elapsed time on the pulse between the 1.5V point on the leading edge and the 1.5V point on the trailing edge or the 1.5V point on the trailing edge and the 1.5V point on the leading edge.

$t_{RISE}$  (Input Rise Time) The elapsed time between the 20% and the 80% point on the leading edge of the input pulse.

$t_{FALL}$  (Input Fall Time) The elapsed time between the 80% and the 20% point on the trailing edge of the input pulse.

$t_{PLH}$  (Time Delay, Rising) The elapsed time between the 1.5V point on the leading edge of the input pulse and the 1.5V point on the leading edge of any TAP output pulse.  $t_{PHL}$  (Time Delay, Falling) The elapsed time between the 1.5V point on the trailing edge of the input pulse and the 1.5V point on the trailing edge of any TAP output pulse.

#### Notes

- 1.) All voltages are referenced to ground.

- 2.) Measured with outputs open, minimum period.

- Vcc=5V @25°C Delays accurate on both rising and falling edges within +/- 2 ns.

- 4.) See Test Conditions (following page).

- 5.) The combination of temperature vari ations between 0°C and 70°C and voltage variations between 4.75 volts and 5.25 volts produce a worst case delay shift of +/- 5%.

## FIGURE 3: DALLAS SEMICONDUCTOR TEST CIRCUIT

### **Test Setup Description**

Figure 3 illustrates the hardware configuration used for measuring the timing parameters on the DS1005. The input waveform is produced by a precision pulse generator under software control. Time delays are measured by a time interval counter (20 ps resolution) connected between the input and each TAP. Each TAP is selected and connected to the counter by a VHF switch control unit.

The measurement setup is calibrated by TDR (time domain reflectometry) techniques. All measurements are fully automated, with each instrument controlled by a central computer over an IEEE 488 bus.

### **Test Conditions**

Input: Ambient Temperature:  $25^{\circ}C_{+}/-3^{\circ}C$ Supply Voltage (Vcc):  $5.0V_{+}/-0.1V$ Input Pulse: High =  $3.0V_{+}/-0.1V$ Low =  $0.0V_{+}/-0.1V$ Source Impedancc:  $50^{\circ}\Omega$  Max. Rise and FAII Time: 3.0 ns Max. (measured between 0.6V and 2.4V) Pulse Width = 500 ns Period= 1us Note:

Above conditions are for test only and do not restrict the operation of the device under other conditions.

### **Output:**

Each output is loaded with a 74F04. Delay is measured at the 1.5V level on the rising and falling edge.

## D.C. ELECTRICAL CHARACTERISTICS

(0°C to 70°C, Vcc = 5.0V +/- 5%)

| PARAMETER                    | SYMBOL          | TEST<br>COND.                            | MIN. | TYP. | MAX. | UNITS | NOTES |

|------------------------------|-----------------|------------------------------------------|------|------|------|-------|-------|

| Supply Voltage               | Vcc             |                                          | 4.75 | 5.00 | 5.25 | v     | 1     |

| High Level<br>Input Voltage  | V <sub>IH</sub> |                                          | 2.2  |      | 5.5  | v     | 1     |

| Low Level<br>Input Voltage   | V <sub>IL</sub> |                                          | -0.5 |      | 0.8  | v     | 1     |

| Input Leakage<br>Current     | l,              | 0.0V <u>←</u> VI <u></u> ∠Vcc            | -1.0 |      | 1.0  | υA    |       |

| Active Current               | Ι <sub>œ</sub>  | Vcc= Max;<br>Period= Min.                |      | 40.0 | 70.0 | mA    | 2     |

| High Level<br>Output Current | l <sub>ot</sub> | Vcc= Min.<br>V <sub>oH</sub> =2.4V       | 1.0  |      | mA   |       |       |

| Low Level<br>Output Current  | l <sub>a</sub>  | Vcc <b>=Min</b><br>V <sub>oL</sub> =0.5V | 12.0 |      |      | mA    |       |

## A.C. ELECTRICAL CHARACTERISTICS

(T<sub>A</sub>= 25°C, Vcc=5V+/- 5%)

| PARAMETER                             | SYMBOL           | MIN.      | TYP.    | MAX.   | UNITS | NOTES |

|---------------------------------------|------------------|-----------|---------|--------|-------|-------|

| Input Pulse Width                     | tw               | 40%ofTAP5 |         |        | ns    |       |

| Input to TAP delay<br>(leading edge)  | t <sub>PLH</sub> | note 3    | Table 1 | note 3 | ns    | 4,5   |

| Input to TAP Delay<br>(trailing edge) | t <sub>PHL</sub> | note 3    | Table 1 | note 3 | ns    | 4,5   |

|                                       | Period           | 4 (tWI)   |         |        | ns    |       |

## CAPACITANCE

(T<sub>A</sub>=25°C)

| PARAMETER          | SYMBOL         | MIN. | TYP. | MAX. | UNITS | NOTES |

|--------------------|----------------|------|------|------|-------|-------|

| Input Capacitance  | C <sub>N</sub> |      | 5    | 10   | pF    |       |

| Output Capacitance | Car            |      | 5    | 10   | pF    |       |

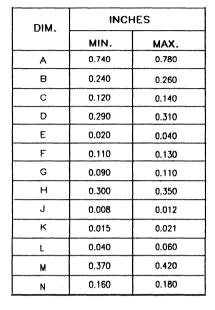

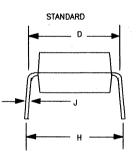

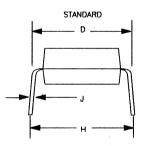

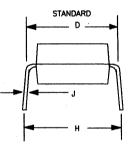

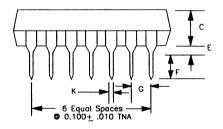

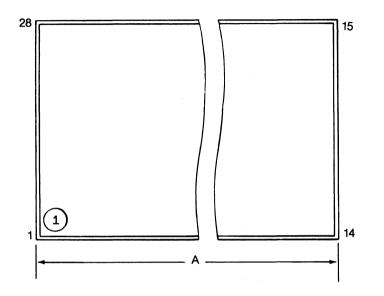

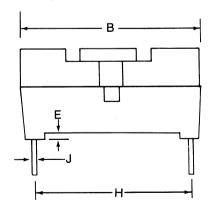

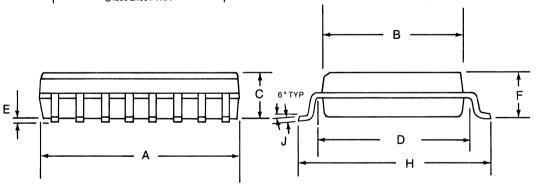

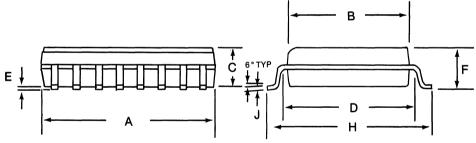

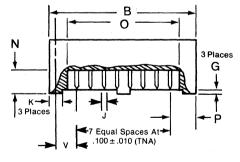

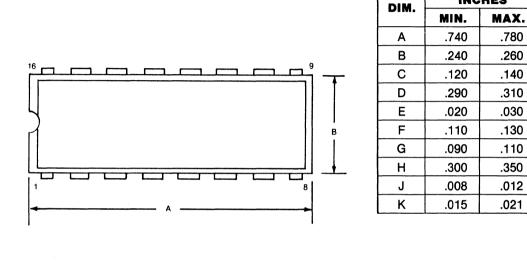

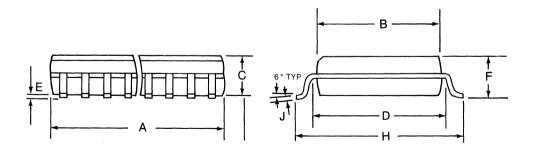

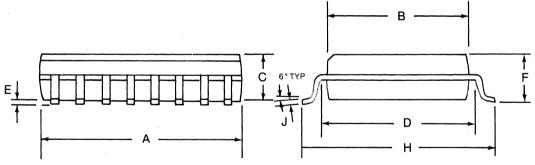

# Silicon Delay Line DS1005 14 Pin DIP

| DIM. | INCHES |       |

|------|--------|-------|

|      | MIN.   | MAX.  |

| A    | 0.740  | 0.780 |

| в    | 0.240  | 0.260 |

| С    | 0.120  | 0.140 |

| D    | 0.290  | 0.310 |

| E    | 0.020  | 0.040 |

| F    | 0.110  | 0.130 |

| G    | 0.090  | 0.110 |

| н    | 0.300  | 0.350 |

| J    | 0.008  | 0.012 |

| к    | 0.015  | 0.021 |

| L    | 0.040  | 0.060 |

| м    | 0.370  | 0.420 |

| N    | 0.160  | 0.180 |

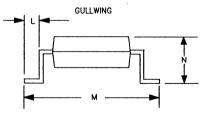

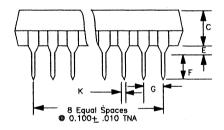

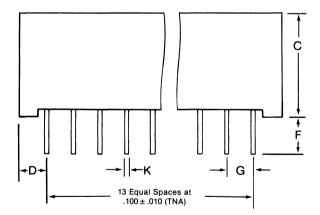

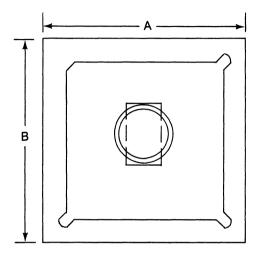

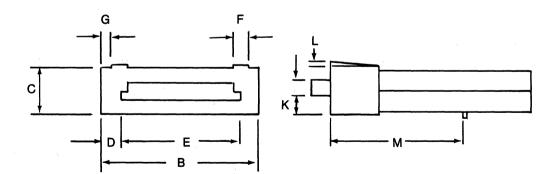

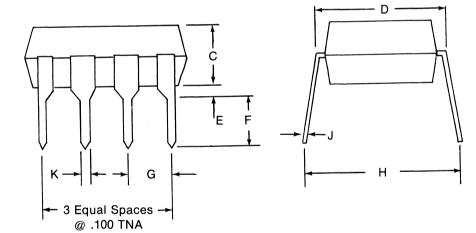

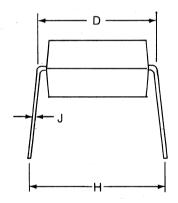

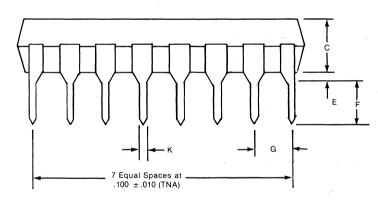

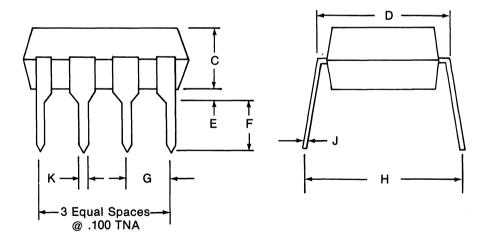

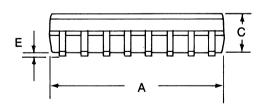

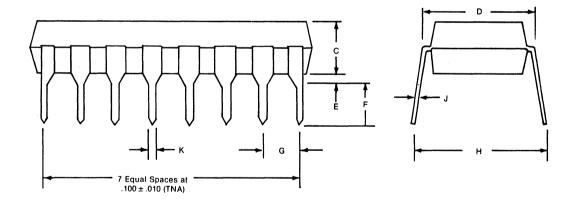

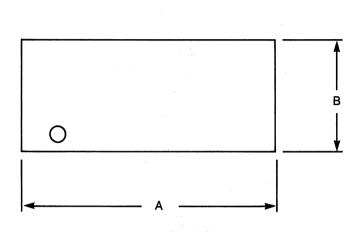

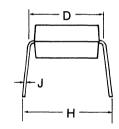

# Silicon Delay Line DS1005M 8 Pin Mini-DIP

| DIM. | INCHES |       |  |

|------|--------|-------|--|

|      | MIN.   | MAX.  |  |

| A    | 0.360  | 0.400 |  |

| в    | 0.240  | 0.260 |  |

| С    | 0.120  | 0.140 |  |

| D    | 0.290  | 0.310 |  |

| E    | 0.020  | 0.040 |  |

| F    | 0.110  | 0.130 |  |

| G    | 0.090  | 0.110 |  |

| н    | 0.300  | 0.350 |  |

| J    | 0.008  | 0.012 |  |

| к    | 0.015  | 0.021 |  |

| L    | 0.040  | 0.060 |  |

| м    | 0.370  | 0.420 |  |

| N    | 0.160  | 0.180 |  |

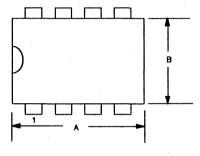

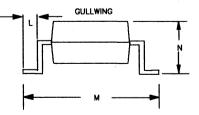

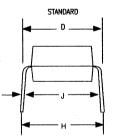

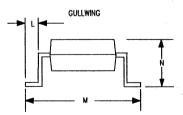

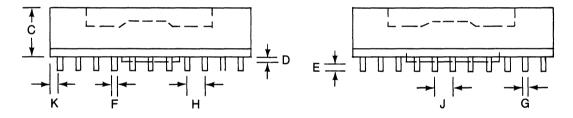

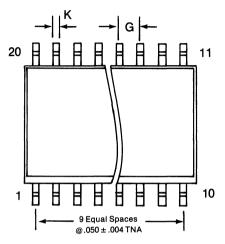

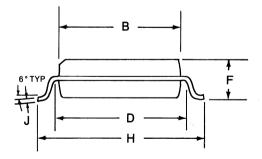

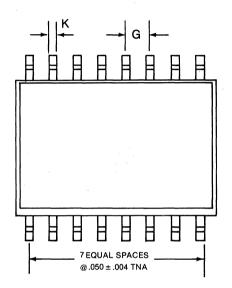

# Silicon Delay Line DS1005S 16 Pin SOIC

| DIM. | INCHE | S    |

|------|-------|------|

|      | MIN.  | MAX. |

| A    | .403  | .411 |

| B    | .290  | .296 |

| с    | .089  | .095 |

| D    | .325  | .330 |

| E    | .008  | .012 |

| F    | .097  | .105 |

| G    | .046  | .054 |

| н    | .402  | .410 |

| J    | .006  | .011 |

| к    | .013  | .019 |

# Dallas Semiconductor 7 In 1 Silicon Delay Line

# PRELIMINARY DS1007 16 Pin DIP DS1007S 16 Pin SOIC

### FEATURES

- All silicon time delay

- 7 independent logic buffered delays

- Accuracy of +/- 2 ns @ 25°C

- Four delays can be custom set between 3 ns and 7 ns

- Three delays can be custom set between 8 ns and 20 ns

- Leading edge precision

- Auto-insertable 16 pin DIP

- Surface mount 16 pin SOIC

- Low power CMOS

- TTL compatible

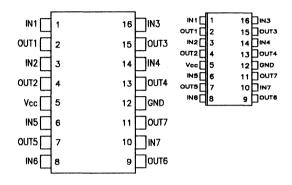

**PIN CONNECTIONS**

#### **PIN NAMES**

| IN1 - IN7 | - Inputs   |

|-----------|------------|

| Out1-Out7 | - Outputs  |

| GND       | - Ground   |

| Vcc       | - +5 Volts |

### DESCRIPTION

The DS1007 Delay Line provides seven independent delay times which are set by Dallas Semiconductor to the customer's specification. The delay times can be set from 3 ns to 20 ns with an accuracy of +/-2 ns at room temperature. The device is offered in both a 16 pin DIP and a 16 pin SOIC. Since the DS1007 is an all silicon solution, better economy and reliability are achieved when compared to older methods using hybrid technology. The DS1007 reproduces the input logic level at the output after the fixed delay as specified by the customer specification.

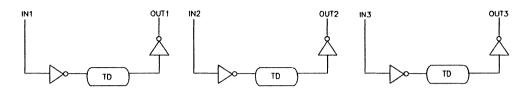

### FIGURE 1: LOGIC DIAGRAM

INPUT PULSE WIDTH > 100% OF DELAY

### TABLE 1: PART NUMBER DELAY TABLE (tpt., tpL)

| INPUT NO. | OUTPUT DELAY |

|-----------|--------------|

| INPUT 1   | 3ns-7ns      |

| INPUT 2   | 3ns-7ns      |

| INPUT 3   | 3ns-7ns      |

| INPUT 4   | 3ns-7ns      |

| INPUT 5   | 8ns-20ns     |

| INPUT 6   | 8ns-20ns     |

| INPUT 7   | 8ns-20ns     |

### **Absolute Maximum Ratings\***

Voltage on any pin to ground: -1.0Vto + 7.0V Operating temperature: 0°C° to 70°C Storage temperature: -55°C to + 125°C Soldering temperature: 260°C for 10 seconds Short circuit output current: 50mA for 1 second

This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

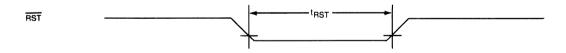

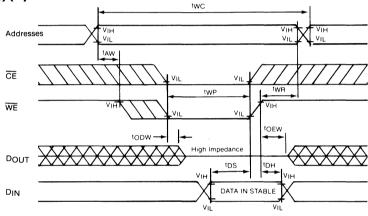

FIGURE 2: TIMING DIAGRAM SILICON DELAY LINE

#### Terminology

<u>Period</u> The time elapsed between the leading edge of the first pulse and the leading edge of the following pulse.

$t_{WI}$  (Pulse Width) The elapsed time on the pulse between the 1.5V point on the leading edge and the 1.5V point on the trailing edge or the 1.5V point on the trailing edge and the 1.5V point on the leading edge.

$t_{RISE}$  (Input Rise Time) The elapsed time between the 20% and the 80% point on the leading edge of the input pulse.

$t_{FALL}$  (Input Fall Time) The elapsed time between the 80% and the 20% point on the trailing edge of the input pulse.  $t_{\rm PLH}$  (Time Delay, Rising) The elapsed time between the 1.5V point on the leading edge of the input pulse and the 1.5V point on the leading edge of any TAP output pulse.

#### Notes

1.) All voltages are referenced to ground.

2.) Measured with outputs open, minimum period.

3.) Vcc=5V @25°C Delays accurate on rising edges within +/- 2 ns.

4.) See Test Conditions (following page).

### FIGURE 3: DALLAS SEMICONDUCTOR TEST CIRCUIT

### **Test Setup Description**

Figure 3 illustrates the hardware configuration used for measuring the timing parameters on the DS1007. The input waveform is produced by a precision pulse generator under software control. Time delays are measured by a time interval counter (20 ps resolution) connected between the input and each TAP. Each TAP is selected and connected to the counter by a VHF switch control unit.

The measurement setup is calibrated by TDR (time domain reflectometry) techniques. All measurements are fully automated, with each instrument controlled by a central computer over an IEEE 488 bus.

### **Test Conditions**

Input: Ambient Temperature: 25°C+/-3°C Supply Voltage (Vcc): 5.0V+/-0.1V Input Pulse: High = 3.0V+/-0.1V Low = 0.0V + -0.1VSource Impedancc: 50 Max. Rise and FAII Time: 3.0 ns Max. (measured between 0.6V and 2.4V) Pulse Width = 100ns Period=200ns Note: Above conditions are for test only and do not

restrict the operation of the device under other conditions.

### **Output:**

Each output is loaded with a 74F04. Delay is measured at the 1.5V level on the rising, edge.

## D.C. ELECTRICAL CHARACTERISTICS

(0°C to 70°C, Vcc = 5.0V+/- 5%)

| PARAMETER                    | SYMBOL<br>COND. | TEST                                | MIN  | ТҮР  | MAX  | UNITS | NOTES |

|------------------------------|-----------------|-------------------------------------|------|------|------|-------|-------|

| Supply Voltage               | Vcc             |                                     | 4.75 | 5.00 | 5.25 | V     | 1     |

| High Level<br>Input Voltage  | V <sub>IH</sub> |                                     | 2.2  |      | 5.5  | V     | 1     |

| Low Level<br>Input Voltage   | V <sub>IL</sub> |                                     | -0.5 |      | 0.8  | V     | 1     |

| Input Leakage<br>Current     | I,              | 0.0V≝VI≦Vcc                         | -1.0 |      | 1.0  | иA    |       |

| Active Current               | Ι <sub>œ</sub>  | Vcc= Max;<br>Period= Min.           |      | 40.0 | 70.0 | mA    | 2     |

| High Level<br>Output Current | I <sub>on</sub> | Vcc= Min.<br>V <sub>oH</sub> = 2.4V | 1.0  |      |      | mA    |       |

| Low Level<br>Output Current  | la              | Vcc= Min.<br>V <sub>oL</sub> = 0.5V | 1.0  |      |      | mA    |       |

## A.C. ELECTRICAL CHARACTERISTICS

$(T_{A} = 25^{\circ}C, Vcc = 5V + - 5\%)$

| PARAMETER                         | SYMBOL              | MIN                  | ТҮР | МАХ    | UNITS | NOTES |

|-----------------------------------|---------------------|----------------------|-----|--------|-------|-------|

| Input Pulse Width                 | t <sub>m</sub> a sa | 100%                 |     |        | ns    |       |

| Input to Output<br>(leading edge) | t <sub>PLH</sub>    | note 3               |     | note 3 | ns    | 4     |

|                                   | Period              | 3 (t <sub>wı</sub> ) |     |        | ns    |       |

### CAPACITANCE

(T<sub>A</sub>= 25°C)

| PARAMETER          | SYMBOL         | MIN | ТҮР | MAX | UNITS | NOTES |

|--------------------|----------------|-----|-----|-----|-------|-------|

| Input Capacitance  | C <sub>N</sub> |     | 5   | 10  | pF    |       |

| Output Capacitance | Car            |     | 5   | 10  | pF    |       |

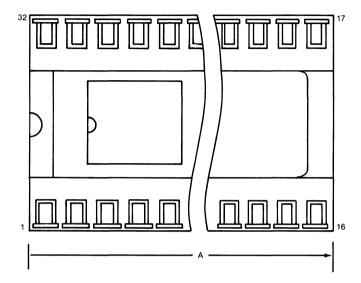

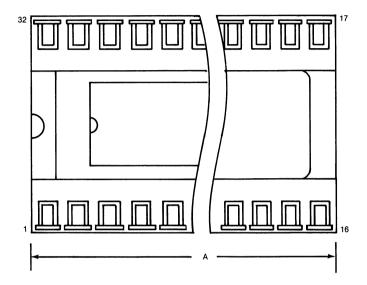

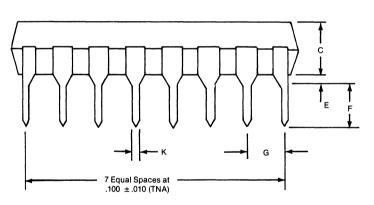

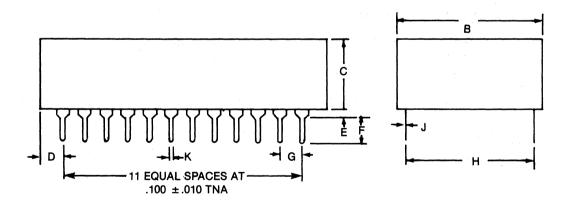

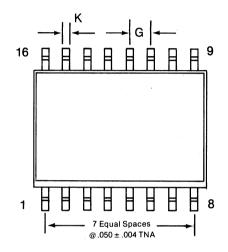

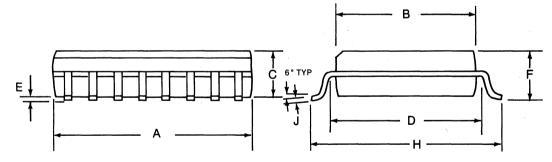

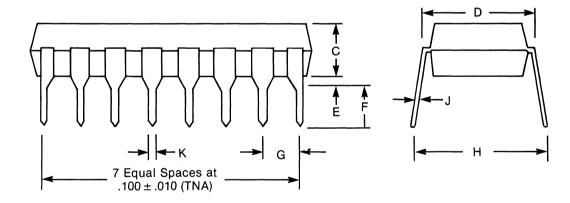

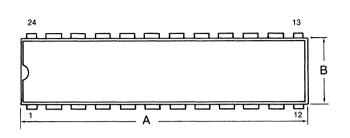

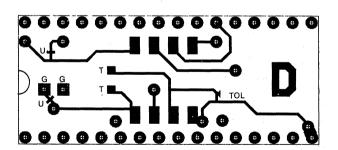

# SILICON DELAY LINE DS1007 16 Pin DIP

\_\_\_\_\_

| DIM. | INCH  | IES   |

|------|-------|-------|

|      | MIN.  | MAX.  |

| А    | 0.740 | 0.780 |

| В    | 0.240 | 0.260 |

| с    | 0.120 | 0.140 |

| D    | 0.290 | 0.310 |

| E    | 0.020 | 0.040 |

| F    | 0.110 | 0.130 |

| G    | 0.090 | 0.110 |

| н    | 0.300 | 0.350 |

| J    | 0.008 | 0.012 |

| к    | 0.015 | 0.021 |

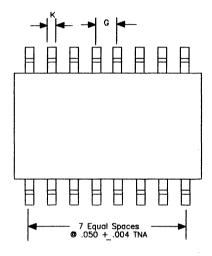

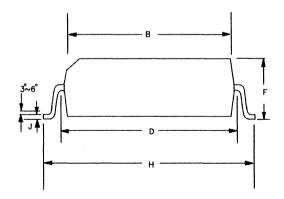

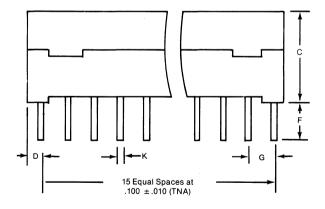

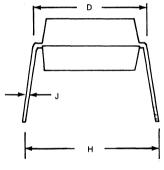

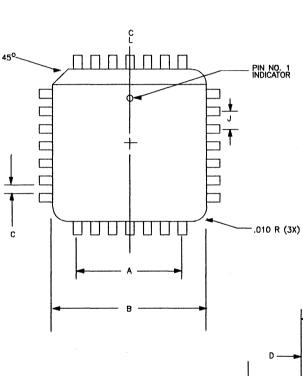

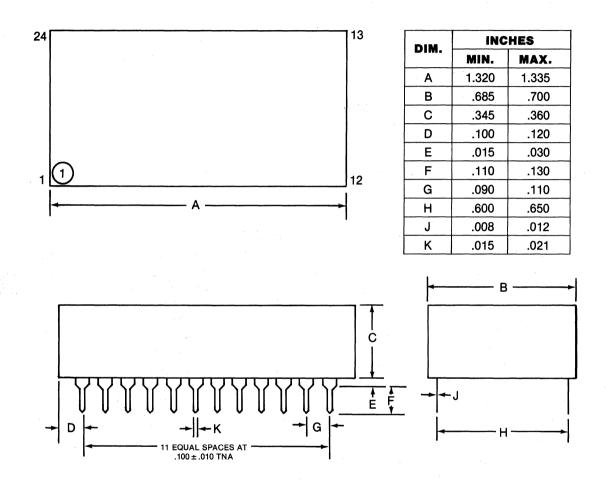

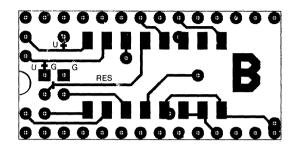

# SILICON DELAY LINE DS1007S 16 Pin SOIC

| DIM. | INCHES |      |  |

|------|--------|------|--|

|      | MIN.   | MAX. |  |

| A    | .403   | .411 |  |

| в    | .290   | .296 |  |

| с    | .089   | .095 |  |

| D    | .325   | .330 |  |

| E    | .008   | .012 |  |

| F    | .097   | .105 |  |

| G    | .046   | .054 |  |

| н    | .402   | .410 |  |

| J    | .006   | .011 |  |

| к    | .013   | .019 |  |

## Dallas Semiconductor 10 TAP Silicon Delay Line

# DS1010 14 Pin DIP DS1010S 16 Pin SOIC

### FEATURES

- All silicon time delay 10 TAPS equally spaced

- Delays are stable and precise

- Leading and trailing edge accuracy

- Standard 14 pin DIP or 16 pin SOIC

- Delay tolerance +/- 5%

- Economical

- Auto-insertable

- Low power CMOS

- TTL compatible

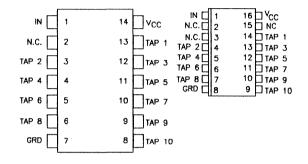

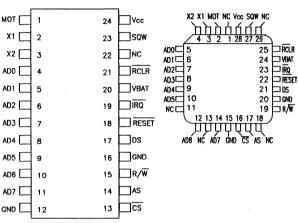

#### **PIN CONNECTIONS**

#### **PIN NAMES**

TAP1-TAP10 - TAP Output NumberVcc- 5 VoltsGND- GroundNC- No ConnectionIN- Input

#### DESCRIPTION

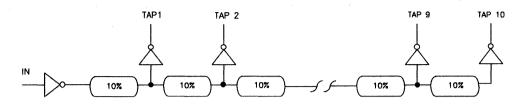

The DS1010 Series Delay Line has ten equally spaced TAPS providing delays from 10 ns to 500 ns. The devices are offered in a standard 14 pin DIP which is pin compatible with hybrid delay lines. Alternatively, a 16 pin SOIC is available for surface mount technology which reduces P.C. board area. Since the DS1010 Series Delay Line is an all silicon solution, better economy is achieved when compared to older methods of using hybrid techniques. The DS1010 Series Delay Lines provide a nominal accuracy of +/- 5% or +/- 2 ns, which ever is greater. The DS1010 Delay Line reproduces the input logic level at the output after a fixed delay as specified by the dash number extension of the part number. The DS1010 is designed to produce both leading and trailing edge with equal precision. Each TAP is capable of driving up to ten 74LS type loads.

### FIGURE 1: LOGIC DIAGRAM

## TABLE 1: PART NUMBER DELAY TABLE (tphi, tplh)

| CATALOG<br>P/N | TOTAL<br>DELAY | DELAY/TAP<br>(NS) |

|----------------|----------------|-------------------|

| DS1010-100     | 100            | 10                |

| DS1010-150     | 150            | 15                |

| DS1010-200     | 200            | 20                |

| DS1010-250     | 250            | 25                |

| DS1010-300     | 300            | 30                |

| DS1010-350     | 350            | 35                |

| DS1010-400     | 400            | 40                |

| DS1010-500     | 500            | 50                |

Absolute Maximum Ratings\* Voltage on any pin to ground: -1.0Vto + 7.0V Operating temperature: 0°C to 70°C Storage temperature: -55°C to + 125°C Soldering temperature: 260°C for 10 seconds Short circuit output current: 50mA for 1 second

\*This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

### FIGURE 2: TIMING DIAGRAM-SILICON DELAY LINE

### Terminology

<u>Period</u> The time elapsed between the leading edge of the first pulse and the leading edge of the following pulse.

$t_{WI}$  (Pulse Width) The elapsed time on the pulse between the 1.5V point on the leading edge and the 1.5V point on the trailing edge or the 1.5V point on the trailing edge and the 1.5V point on the leading edge.

$t_{\text{RISE}}$  (Input Rise Time) The elapsed time between the 20% and the 80% point on the leading edge of the input pulse.

$t_{FALL}$  (Input Fall Time) The elapsed time between the 80% and the 20% point on the trailing edge of the input pulse.

$t_{PLH}$  (Time Delay, Rising) The elapsed time between the 1.5V point on the leading edge of the input pulse and the 1.5V point on the leading edge of any TAP output pulse.  $t_{\rm PHL}$  (Time Delay, Falling) The elapsed time between the 1.5V point on the trailing edge of the input pulse and the 1.5V point on the trailing edge of any TAP output pulse.

#### Notes

- 1.) All voltages are referenced to ground.

- 2.) Measured with outputs open, minimum period.

- Vcc=5V @25°C Delays accurate on both rising and falling edges within +/- 2 ns,or 5%.

- 4.) See Test Conditions (following page).

55

### FIGURE 3: DALLAS SEMICONDUCTOR TEST CIRCUIT

#### **Test Setup Description**

Figure 3 illustrates the hardware configuration used for measuring the timing parameters on the DS1010. The input waveform is produced by a precision pulse generator under software control. Time delays are measured by a time interval counter (20 ps resolution) connected between the input and each TAP. Each TAP is selected and connected to the counter by a VHF switch control unit.

The measurement setup is calibrated by TDR (time domain reflectometry) techniques. All measurements are fully automated, with each instrument controlled by a central computer over an IEEE 488 bus.

#### Test Conditions Input:

Ambient Temperature: 25°C+/-3° Supply Voltage (Vcc): 5.0V+/-0.1V Input Pulse: High=3.0V+/-0.1V Low = 0.0V+/-0.1V Source Impedancc: 50∩Max. Rise and FAII Time: 3.0 ns Max. (measured between 0.6V and 2.4V) Pulse Width = 500 ns Period= 1us Note:

Above conditions are for test only and do not restrict the operation of the device under other conditions.

### Output:

Each output is loaded with a 74F04. delay is measured at the 1.5V level on the rising and falling edge.

## D.C. ELECTRICAL CHARACTERISTICS

### (0°C to 70°C,Vcc= 5.0V +/- 5%)

| PARAMETER                    | SYMBOL          | TEST<br>COND.                              | MIN. | ТҮР. | MAX. | UNITS | NOTES |

|------------------------------|-----------------|--------------------------------------------|------|------|------|-------|-------|

| Supply Voltage               | Vcc             |                                            | 4.75 | 5.00 | 5.25 | v     | 1     |

| High Level<br>Input Voltage  | V <sub>IH</sub> |                                            | 2.2  |      | 5.5  | V     | 1     |

| Low Level<br>Input Voltage   | V <sub>IL</sub> |                                            | -0.5 |      | 0.8  | v     | 1     |

| Input Leakage<br>Current     | I <sub>L</sub>  | 0.0¥≝V <sub>/</sub> ⊒V <sub>∞</sub>        | -1.0 |      | 1.0  | uA    |       |

| Active Current               | Ι <sub>œ</sub>  | Vcc=Max:<br>Period=Min.                    |      | 40.0 | 75.0 | mA    | 2     |

| High Level<br>Output Current | I <sub>OH</sub> | Vcc <b>=Min</b> .<br>V <sub>он</sub> =2.4V | 1.0  |      |      | mA    |       |

| Low Level<br>Output Current  | I <sub>a</sub>  | Vcc=Min.<br>V <sub>oL</sub> =0.5V          | 12.0 |      |      | mA    |       |

## A.C ELECTRICAL CHARACTERISTICS

# (T<sub>A</sub>= 25°C, Vcc= 5V +/- 5%)

| PARAMETER                             | SYMBOL           | MIN.               | TYP.    | MAX.   | UNITS | NOTES |

|---------------------------------------|------------------|--------------------|---------|--------|-------|-------|

| Input Pulse Width                     | t <sub>w</sub>   | 30% of<br>TAP 10   |         |        | ns    |       |

| Input to TAP Delay<br>(leading edge)  | t <sub>PLH</sub> | note 3             | Table 1 | note 3 | ns    | 4     |

| Input to TAP Delay<br>(trailing edge) | t <sub>PHL</sub> | note 3             | Table 1 | note 3 | ns    | 4     |

|                                       | Period           | 3(t <sub>w</sub> ) |         |        | ns    |       |

### CAPACITANCE

(T<sub>A</sub>= 25°C)

| PARAMETER          | SYMBOL | MIN. | TYP. | MAX. | UNITS | NOTES |

|--------------------|--------|------|------|------|-------|-------|

| Input Capacitance  | CIN    |      | 5    | 10   | рF    |       |

| Output Capacitance | COUT   |      | 5    | 10   | pF    |       |

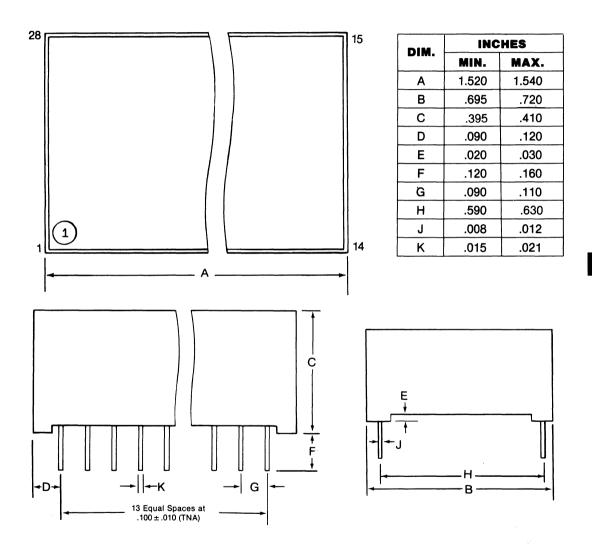

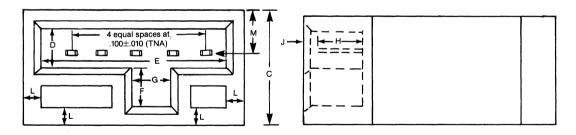

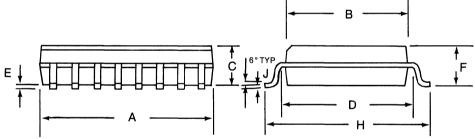

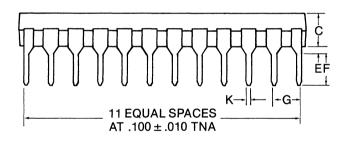

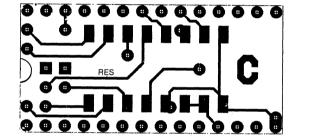

# Silicon Delay Line DS1010 14 Pin DIP

| DIM. | INCH  | IES   |

|------|-------|-------|

|      | MIN.  | MAX.  |

| A    | 0.740 | 0.780 |

| в    | 0.240 | 0.260 |

| С    | 0.120 | 0.140 |

| D    | 0.290 | 0.310 |

| E    | 0.020 | 0.040 |

| F    | 0.110 | 0.130 |

| G    | 0.090 | 0.110 |

| н    | 0.300 | 0.350 |

| J    | 0.008 | 0.012 |

| к    | 0.015 | 0.021 |

| L    | 0.040 | 0.060 |

| м    | 0.370 | 0.420 |

| N    | 0.160 | 0.180 |

58

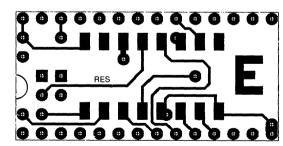

# Silicon Delay Line DS1010S 16 Pin SOIC

| DIM. | INCHES |      |  |

|------|--------|------|--|

|      | MIN.   | MAX. |  |

| А    | .403   | .411 |  |

| В    | .290   | .296 |  |

| с    | .089   | .095 |  |

| D    | .325   | .330 |  |

| E    | .008   | .012 |  |

| F    | .097   | .105 |  |

| G    | .046   | .054 |  |

| н    | .402   | .410 |  |

| J    | .006   | .011 |  |

| к    | .013   | .019 |  |

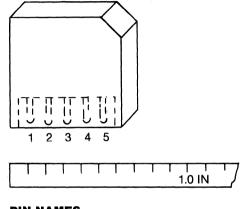

# Dallas Semiconductor 3 In 1 Silicon Delay Line

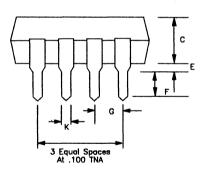

# DS1013 14 Pin DIP DS1013M 8 Pin DIP DS1013S 16 Pin SOIC

### FEATURES

- All silicon time delay

- 3 independent logic buffered delays

- Delay tolerance +/- 2 ns

- Stable and precise over temperature and voltage range

- Leading and trailing edge accuracy

- Standard 14 pin DIP, 8 pin MINI-DIP or 16 pin SOIC

- Auto-insertable

- Low power CMOS

- TTL compatible

### **PIN CONNECTIONS**

#### **PIN NAMES**

| IN1, IN2, IN3    | - Inputs   |

|------------------|------------|

| Out1, Out2, Out3 | - Outputs  |

| GND              | - Ground   |

| Vcc              | - +5 Volts |

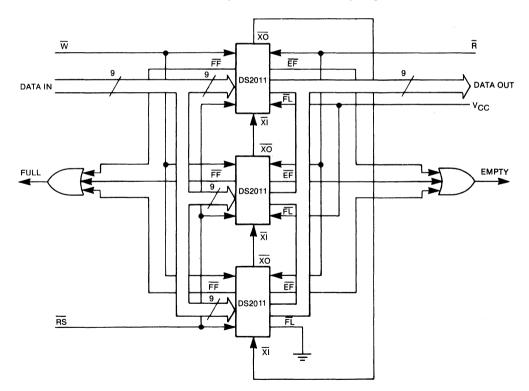

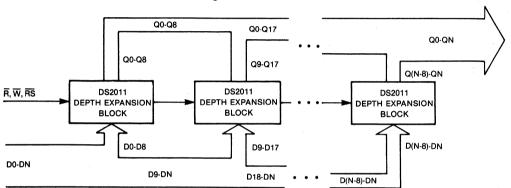

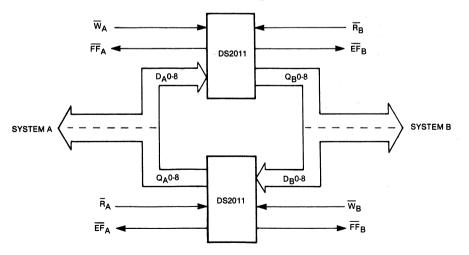

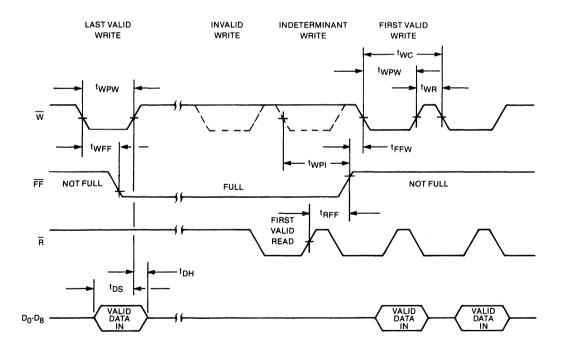

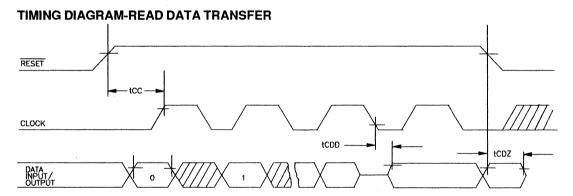

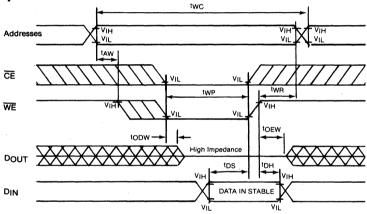

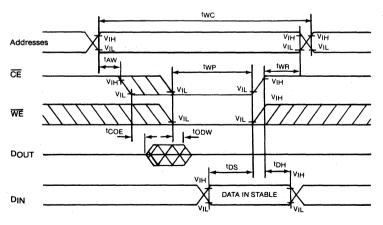

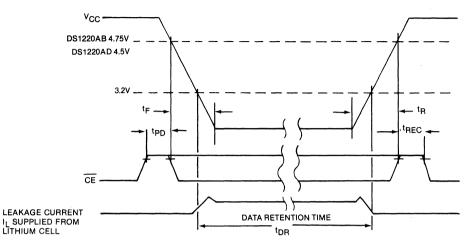

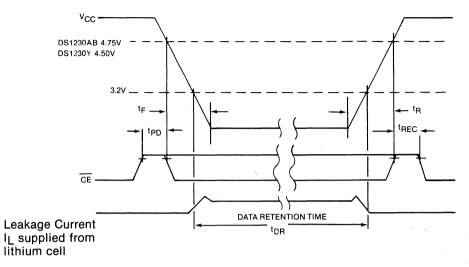

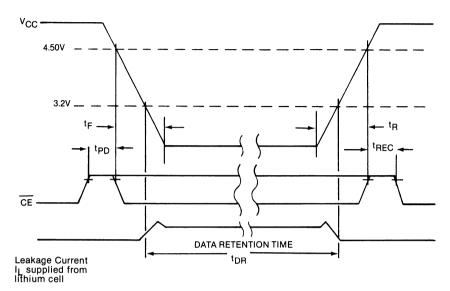

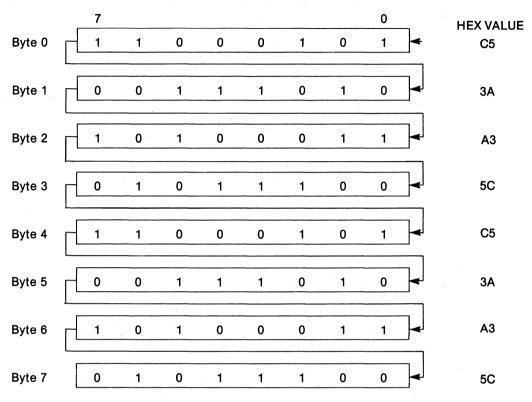

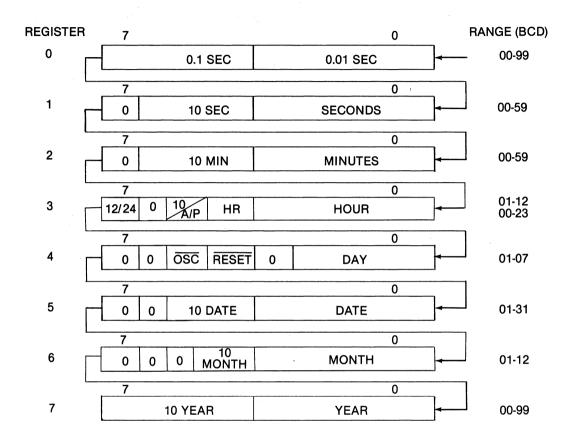

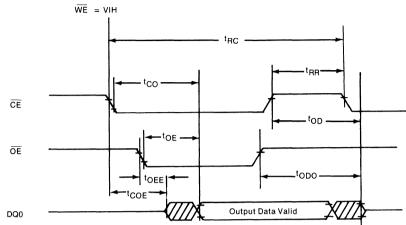

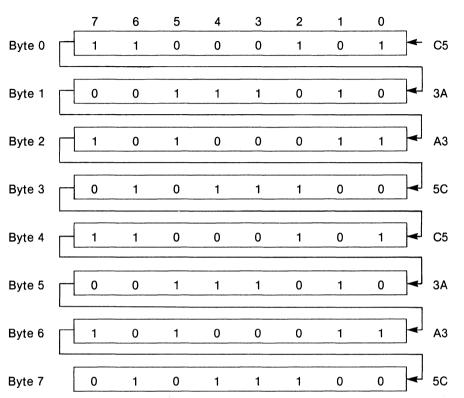

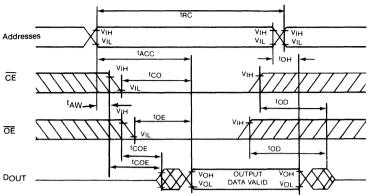

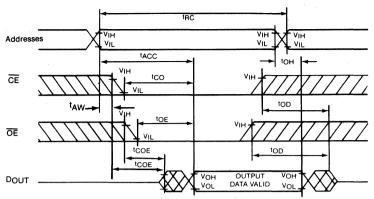

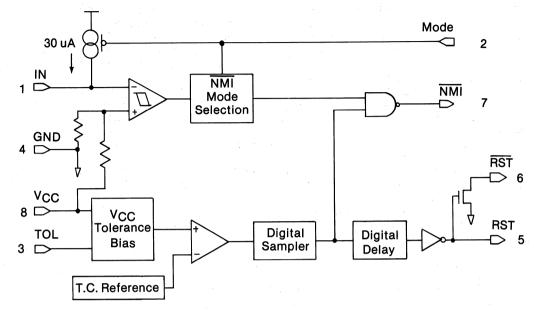

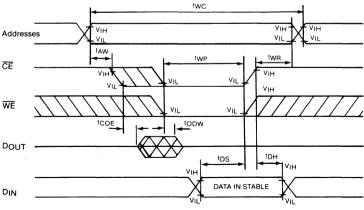

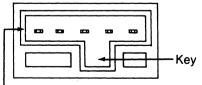

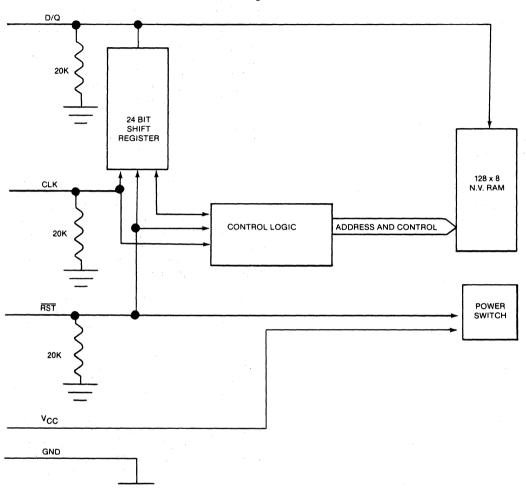

### DESCRIPTION